| –ź–≤—ā–ĺ—Ä |

–°–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł–Ķ |

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

|

–ė–≥—Ä—č —Ā –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–ľ–ł —Ä–Ķ–≥–ł—Ā—ā—Ä–į–ľ–ł –≤ —Ü–Ķ–Ľ—Ź—Ö —É–Ľ—É—á—ą–ł—ā—Ć –Ņ–ĺ–ļ–į–∑–į—ā–Ķ–Ľ–ł –≤ —Ā–ł–Ĺ—ā–Ķ—ā–ł—á–Ķ—Ā–ļ–ł—Ö —ā–Ķ—Ā—ā–į—Ö –≤ –ļ–ĺ–Ĺ–Ķ—á–Ĺ–ĺ–ľ –ł—ā–ĺ–≥–Ķ –Ĺ–Ķ –ī–į—é—ā –Ņ—Ä–į–ļ—ā–ł—á–Ķ—Ā–ļ–ĺ–Ļ –Ņ–ĺ–Ľ—Ć–∑—č. –ē—Ā–Ľ–ł —Ä–į–∑–ĺ–Ī—Ä–į—ā—Ć—Ā—Ź, –≤ –ł—ā–ĺ–≥–Ķ —ć—ā–ĺ –Ņ—Ä–ł–≤–ĺ–ī–ł—ā –ļ –ī–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ł—é –į–Ņ–Ņ–į—Ä–į—ā–Ĺ–ĺ–≥–ĺ —Ź–ī—Ä–į, –ļ–ĺ—ā–ĺ—Ä–ĺ–Ķ –ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –ĺ—Ā–Ĺ–ĺ–≤–Ĺ—É—é —Ä–į–Ī–ĺ—ā—É, –ł —ā—É—ā –Ķ–≥–ĺ —Ā—ā–ĺ–ł—ā –į–ļ–ļ—É—Ä–į—ā–Ĺ–ĺ "–ĺ—ā—Ü–Ķ–Ņ–ł—ā—Ć" –ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į, —á—ā–ĺ–Ī—č –Ĺ–Ķ –ī–Ķ–Ľ–į—ā—Ć –ł–∑ —É–Ĺ–ł–≤–Ķ—Ä—Ā–į–Ľ—Ć–Ĺ–ĺ–≥–ĺ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā, –ļ–ĺ—ā–ĺ—Ä—č–Ļ –Ņ–ĺ —Ā—É—ā–ł –Ī—É–ī–Ķ—ā –ļ—Ä—É—ā–ł—ā—Ć—Ā—Ź –≤ —Ü–ł–ļ–Ľ–Ķ CMD1 CMD2. –í –Ņ—Ä–ł–Ĺ—Ü–ł–Ņ–Ķ –Ķ—Ā—ā—Ć –≤–į—Ä–ł–į–Ĺ—ā—č —É—Ā–ļ–ĺ—Ä–Ķ–Ĺ–ł—Ź —Ü–ł–ļ–Ľ–ĺ–≤ –ł —á–į—Ā—ā–ĺ –≤—Ā—ā—Ä–Ķ—á–į—é—ā—Ā—Ź –ī–ĺ–Ņ–ĺ–Ľ–Ĺ–ł—ā–Ķ–Ľ—Ć–Ĺ—č–Ķ —Ą–Ľ–į–≥–ł "–ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —ć—ā–ĺ–Ļ –ļ–ĺ–ľ–į–Ĺ–ī–ĺ–Ļ –ī–Ķ–Ľ–į—ā—Ć ret". –Ě–ĺ —ā–į–ļ–ł–Ķ —Ą–Ľ–į–≥–ł –Ĺ–į—á–ł–Ĺ–į—é—ā —Ä–į—Ā–Ņ–ĺ–Ľ–∑–į—ā—Ć—Ā—Ź –Ņ–ĺ —Ā–ł—Ā—ā–Ķ–ľ–Ķ –ļ–ĺ–ľ–į–Ĺ–ī, –Ņ–ĺ—Ä—ā—Ź –Ķ–Ķ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ—é—é —Ā–ĺ–≥–Ľ–į—Ā–ĺ–≤–į–Ĺ–Ĺ–ĺ—Ā—ā—Ć.

–ė–≥—Ä—č —Ā –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–ľ–ł —Ä–Ķ–≥–ł—Ā—ā—Ä–į–ľ–ł –≤ —Ü–Ķ–Ľ—Ź—Ö —É–Ľ—É—á—ą–ł—ā—Ć –Ņ–ĺ–ļ–į–∑–į—ā–Ķ–Ľ–ł –≤ —Ā–ł–Ĺ—ā–Ķ—ā–ł—á–Ķ—Ā–ļ–ł—Ö —ā–Ķ—Ā—ā–į—Ö –≤ –ļ–ĺ–Ĺ–Ķ—á–Ĺ–ĺ–ľ –ł—ā–ĺ–≥–Ķ –Ĺ–Ķ –ī–į—é—ā –Ņ—Ä–į–ļ—ā–ł—á–Ķ—Ā–ļ–ĺ–Ļ –Ņ–ĺ–Ľ—Ć–∑—č. –ē—Ā–Ľ–ł —Ä–į–∑–ĺ–Ī—Ä–į—ā—Ć—Ā—Ź, –≤ –ł—ā–ĺ–≥–Ķ —ć—ā–ĺ –Ņ—Ä–ł–≤–ĺ–ī–ł—ā –ļ –ī–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ł—é –į–Ņ–Ņ–į—Ä–į—ā–Ĺ–ĺ–≥–ĺ —Ź–ī—Ä–į, –ļ–ĺ—ā–ĺ—Ä–ĺ–Ķ –ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –ĺ—Ā–Ĺ–ĺ–≤–Ĺ—É—é —Ä–į–Ī–ĺ—ā—É, –ł —ā—É—ā –Ķ–≥–ĺ —Ā—ā–ĺ–ł—ā –į–ļ–ļ—É—Ä–į—ā–Ĺ–ĺ "–ĺ—ā—Ü–Ķ–Ņ–ł—ā—Ć" –ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į, —á—ā–ĺ–Ī—č –Ĺ–Ķ –ī–Ķ–Ľ–į—ā—Ć –ł–∑ —É–Ĺ–ł–≤–Ķ—Ä—Ā–į–Ľ—Ć–Ĺ–ĺ–≥–ĺ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā, –ļ–ĺ—ā–ĺ—Ä—č–Ļ –Ņ–ĺ —Ā—É—ā–ł –Ī—É–ī–Ķ—ā –ļ—Ä—É—ā–ł—ā—Ć—Ā—Ź –≤ —Ü–ł–ļ–Ľ–Ķ CMD1 CMD2. –í –Ņ—Ä–ł–Ĺ—Ü–ł–Ņ–Ķ –Ķ—Ā—ā—Ć –≤–į—Ä–ł–į–Ĺ—ā—č —É—Ā–ļ–ĺ—Ä–Ķ–Ĺ–ł—Ź —Ü–ł–ļ–Ľ–ĺ–≤ –ł —á–į—Ā—ā–ĺ –≤—Ā—ā—Ä–Ķ—á–į—é—ā—Ā—Ź –ī–ĺ–Ņ–ĺ–Ľ–Ĺ–ł—ā–Ķ–Ľ—Ć–Ĺ—č–Ķ —Ą–Ľ–į–≥–ł "–ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —ć—ā–ĺ–Ļ –ļ–ĺ–ľ–į–Ĺ–ī–ĺ–Ļ –ī–Ķ–Ľ–į—ā—Ć ret". –Ě–ĺ —ā–į–ļ–ł–Ķ —Ą–Ľ–į–≥–ł –Ĺ–į—á–ł–Ĺ–į—é—ā —Ä–į—Ā–Ņ–ĺ–Ľ–∑–į—ā—Ć—Ā—Ź –Ņ–ĺ —Ā–ł—Ā—ā–Ķ–ľ–Ķ –ļ–ĺ–ľ–į–Ĺ–ī, –Ņ–ĺ—Ä—ā—Ź –Ķ–Ķ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ—é—é —Ā–ĺ–≥–Ľ–į—Ā–ĺ–≤–į–Ĺ–Ĺ–ĺ—Ā—ā—Ć.

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°–Ī –ľ–į—Ä 23, 2024 22:27 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

–ď–Ľ—Ź–Ĺ—É–Ľ –ł—Ö –ļ–ĺ–ī —á—É—ā—Ć –Ņ–ĺ–≤–Ĺ–ł–ľ–į—ā–Ķ–Ľ—Ć–Ĺ–Ķ–Ķ. –ö–ĺ–ī: address opcode label comment

001000 5715C INNER n push n push 1000 0 DO

001001 003E8 1000

001002 00000 0

001003 57D58 IN1 n drop n pop 34 DROP

001004 00022 34

001005 00001 1

001006 BE37B + pop over over INC loop counter

001007 A080A xor T0 IN2 COMPARE

001008 FF39E drop push push nop

00100A FFFFE IN2 drop drop drop ; FINISH

00100B 5715C BENCH n push n push 1000 0 DO

00100C 003E8 1000

00100D 00000 0

00100E 20000 BE1 call INNER

00100F 563DE n pop nop nop

001010 00001 1

001011 BE37B + pop over over INC counter

001012 A0815 xor T0 BE2 COMPARE

001013 FF39E drop push push nop

001014 00003 jmp BE1 LOOP

001015 FFFBA BE2 drop drop drop n FINISH

001016 00007 7

001017 57020 n push ; long call and return

001018 03987 lit' EMIT –Ę–į–ľ –ľ–Ĺ–ĺ–≥–ĺ –ĺ–Ņ–Ķ—á–į—ā–ĺ–ļ, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –ĺ—ā—Ā—É—ā—Ā—ā–≤—É–Ķ—ā —Ā—ā—Ä–ĺ–ļ–į —Ā –į–ī—Ä–Ķ—Ā–ĺ–ľ 001009 (—ā–į–ľ –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ī—č—ā—Ć jmp IN1), –Ņ–ĺ –į–ī—Ä–Ķ—Ā—É 001014 –į–ī—Ä–Ķ—Ā –Ņ—Ä—č–∂–ļ–į –Ĺ–Ķ–Ņ—Ä–į–≤–ł–Ľ—Ć–Ĺ—č–Ļ (–ī–ĺ–Ľ–∂–Ķ–Ĺ –Ī—č—ā—Ć –Ņ—Ä—č–∂–ĺ–ļ –Ņ–ĺ –į–ī—Ä–Ķ—Ā—É XXXE, –į –Ĺ–Ķ XXX3, –≤–ł–ī–ł–ľ–ĺ, –Ĺ–Ķ–Ņ—Ä–į–≤–ł–Ľ—Ć–Ĺ–ĺ —Ä–į—Ā–Ņ–ĺ–∑–Ĺ–į–Ľ–ĺ—Ā—Ć –Ņ—Ä–ł —Ā–ļ–į–Ĺ–ł—Ä–ĺ–≤–į–Ĺ–ł–ł  ), –ī–į –ł —Ą–ĺ—Ä–ľ–į—ā –ļ–ĺ–ľ–į–Ĺ–ī—č –≤—č–∑—č–≤–į–Ķ—ā –Ĺ–Ķ–ļ–ĺ—ā–ĺ—Ä—č–Ķ —Ā–ĺ–ľ–Ĺ–Ķ–Ĺ–ł—Ź. –Ě–į –≥–Ľ–į–∑ —ā–į–ľ –≤–ĺ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–Ķ–ľ —Ü–ł–ļ–Ľ–Ķ 15-20 –ļ–ĺ–ľ–į–Ĺ–ī, –Ĺ–ĺ —Ā–Ľ–ĺ–∂–Ĺ–ĺ –≤ —ā–į–ļ–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ –ĺ—Ü–Ķ–Ĺ–ł–≤–į—ā—Ć, –Ķ—Ā–Ľ–ł –Ĺ–Ķ –∑–Ĺ–į—ā—Ć, —Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —ā–į–ļ—ā–ĺ–≤ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź –ļ–į–∂–ī–į—Ź –ļ–ĺ–ľ–į–Ĺ–ī–į, –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –Ľ–ł –ĺ–Ĺ–ł –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ –ł —ā.–ī. –° –ī—Ä—É–≥–ĺ–Ļ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č —É –Ĺ–į—Ā –Ķ—Ā—ā—Ć —ā–į–ļ—ā–ĺ–≤–į—Ź —á–į—Ā—ā–ĺ—ā–į –ł –≤—Ä–Ķ–ľ—Ź –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł—Ź –ľ–ł–Ľ–Ľ–ł–ĺ–Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł–Ļ. –°–ľ–Ķ–Ľ–ĺ –Ņ–Ķ—Ä–Ķ–ľ–Ĺ–ĺ–∂–į–Ķ–ľ –ĺ–ī–Ĺ–ĺ –Ĺ–į –ī—Ä—É–≥–ĺ–Ķ - –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–ĺ —ā–į–ļ—ā–ĺ–≤ –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –≤–ĺ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–Ķ–ľ —Ü–ł–ļ–Ľ–Ķ: 200*0.17=34 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é —Ü–ł–ļ–Ľ–į –≤ INNER. –Ē–Ľ—Ź —Ā—Ä–į–≤–Ĺ–Ķ–Ĺ–ł—Ź 68040 –ł R4000 —ā—Ä–į—ā—Ź—ā –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –ī–ĺ—Ā—ā–ĺ–Ļ–Ĺ—č–Ķ 9 –ł 12 —ā–į–ļ—ā–ĺ–≤ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, –ī–į –ī–į–∂–Ķ 68030 —Ā –Ķ–≥–ĺ 18 —ā–į–ļ—ā–į–ľ–ł –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –Ĺ–Ķ —ā–į–ļ —É–∂ –ł –Ņ–Ľ–ĺ—Ö. –°–ĺ–∑–ī–į—ā–Ķ–Ľ–ł F21 –Ņ—č—ā—é—ā—Ā—Ź –≤—č–Ļ—ā–ł –ł–∑ –Ņ–ĺ–Ľ–ĺ–∂–Ķ–Ĺ–ł—Ź –ł —Ä–į–∑–≤–ĺ—Ä–į—á–ł–≤–į—é—ā –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ļ —Ü–ł–ļ–Ľ, —É–Ī–ł—Ä–į—Ź —ā–Ķ–ľ —Ā–į–ľ—č–ľ –Ĺ–į–ļ–Ľ–į–ī–Ĺ—č–Ķ —Ä–į—Ā—Ö–ĺ–ī—č –Ĺ–į –ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—é —Ü–ł–ļ–Ľ–į, –≤ —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–Ķ –≤ –ĺ–Ī—Č–Ķ–ľ-—ā–ĺ –Ņ—Ä–ĺ—Ā—ā–ĺ–Ļ –ļ–ĺ–ī –∂–ł—Ä–Ķ–Ķ—ā –į–∂ –ī–ĺ 400 –Ī–į–Ļ—ā, –Ĺ–ĺ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–ĺ —ā–į–ļ—ā–ĺ–≤ –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é —É–ľ–Ķ–Ĺ—Ć—ą–į–Ķ—ā—Ā—Ź –≤—Ā–Ķ–≥–ĺ –Ľ–ł—ą—Ć –ī–ĺ 15. –ė –Ľ–ł—ą—Ć –ļ–ĺ–≥–ī–į –ĺ–Ĺ–ł –∑–į–ī–Ķ–Ļ—Ā—ā–≤—É—é—ā –≤–ľ–Ķ—Ā—ā–ĺ —á–Ķ—Ā—ā–Ĺ–ĺ–≥–ĺ –Ľ–ł—ā–Ķ—Ä–į–Ľ–į —Ā–≤–ĺ–Ļ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ļ —Ä–Ķ–≥–ł—Ā—ā—Ä –ź (–≤—Ä—É—á–Ĺ—É—é –ł–Ľ–ł –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–į–ľ —Ā–ĺ–ĺ–Ī—Ä–į–∑–ł–Ľ?), —ā–ĺ –Ņ–ĺ–Ľ—É—á–į—é—ā –ļ–ĺ—Ā–ľ–ł—á–Ķ—Ā–ļ–ł–Ķ 2 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é.  –ź —É –ľ–Ķ–Ĺ—Ź, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –≤ –Ī–į–∑–ĺ–≤–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ —Ā 6-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł –Ľ–ł—ā–Ķ—Ä–į–Ľ –≤–Ķ—Ā–ł—ā 2 –ļ–ĺ–ľ–į–Ĺ–ī—č (–ł —ā–į–ļ—ā–į), –Ķ—Č–Ķ —ā–į–ļ—ā –Ĺ–į drop, –Ĺ—É –ł –Ķ—Č–Ķ –ĺ–ī–ł–Ĺ –Ĺ–į loop. –í —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–Ķ –ł—ā–Ķ—Ä–į—Ü–ł—Ź –≤–Ķ—Ā–ł—ā 3 –Ī–į–Ļ—ā–į –ł –ī–Ľ–ł—ā—Ā—Ź 4 —ā–į–ļ—ā–į. –ź –≤ –Ņ—Ä–ĺ–ī–≤–ł–Ĺ—É—ā–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ (4- –ł 6-–Ī–ł—ā–Ĺ–ĺ–ľ) –≤—Ā–Ķ–≥–ĺ –ī–≤–į —ā–į–ļ—ā–į: –Ņ–Ķ—Ä–≤—č–Ļ –Ĺ–į 34+drop, –į –≤—ā–ĺ—Ä–ĺ–Ļ –Ĺ–į loop. –ü—Ä–ł –∂–Ķ–Ľ–į–Ĺ–ł–ł, –Ĺ–į–≤–Ķ—Ä–Ĺ–ĺ–Ķ, –ľ–ĺ–∂–Ĺ–ĺ –ł –≤ –ĺ–ī–ł–Ĺ —ā–į–ļ—ā —É–Ľ–ĺ–∂–ł—ā—Ć—Ā—Ź. –ė –ī–į, –ļ–ĺ–ľ–į–Ĺ–ī—č –ī–Ľ—Ź —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –į–Ņ–Ņ–į—Ä–į—ā–Ĺ—č—Ö —Ü–ł–ļ–Ľ–ĺ–≤ - —ć—ā–ĺ (—Ā –ĺ–≥–ĺ–≤–ĺ—Ä–ļ–į–ľ–ł) —É—Ā–Ľ–ĺ–≤–Ĺ—č–Ķ call –ł ret. –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, while –ł do –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –ľ–ĺ–∂–Ĺ–ĺ –ĺ–Ī–ĺ–∑–≤–į—ā—Ć —É—Ā–Ľ–ĺ–≤–Ĺ—č–ľ call, –į repeat –ł loop - —É—Ā–Ľ–ĺ–≤–Ĺ—č–ľ–ł ret. –†–į–∑–Ĺ–ł—Ü–į –Ľ–ł—ą—Ć –≤ —ā–ĺ–ľ, —á—ā–ĺ –ĺ–ī–Ĺ–ł –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—é—ā –ł –ľ–Ķ–Ĺ—Ź—é—ā —Ā—á–Ķ—ā—á–ł–ļ —Ü–ł–ļ–Ľ–į, –į –ī—Ä—É–≥–ł–Ķ –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—é—ā —É—Ā–Ľ–ĺ–≤–ł–Ķ. –£—Ā–Ľ–ĺ–≤–Ĺ—č–ľ call –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ –Ņ–ĺ–Ľ–Ĺ—č–Ļ –Ľ–ł—ā–Ķ—Ä–į–Ľ (–į–ī—Ä–Ķ—Ā, –Ņ–ĺ –ļ–ĺ—ā–ĺ—Ä–ĺ–ľ—É –Ņ—Ä—č–≥–į—ā—Ć –Ņ—Ä–ł –Ĺ–Ķ–≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–ł —É—Ā–Ľ–ĺ–≤–ł—Ź), –Ĺ–ĺ –ĺ–Ĺ–ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –Ľ–ł—ą—Ć —Ä–į–∑ –≤ –ļ–į—á–Ķ—Ā—ā–≤–Ķ –Ņ—Ä–ĺ–Ľ–ĺ–≥–į –Ņ–Ķ—Ä–Ķ–ī –≤—Ö–ĺ–ī–ĺ–ľ –≤ —ā–Ķ–Ľ–ĺ —Ü–ł–ļ–Ľ–į, –į —É—Ā–Ľ–ĺ–≤–Ĺ—č–Ķ ret –Ľ–ł—ā–Ķ—Ä–į–Ľ–ĺ–≤ –Ĺ–Ķ —ā—Ä–Ķ–Ī—É—é—ā (–į–ī—Ä–Ķ—Ā –Ĺ–į—á–į–Ľ–į —Ü–ł–ļ–Ľ–į –Ī–Ķ—Ä—É—ā –ł–∑ —Ā—ā–Ķ–ļ–į –≤–ĺ–∑–≤—Ä–į—ā–ĺ–≤) –ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –∑–į —ā–į–ļ—ā. –ď–Ľ—Ź–Ĺ—É–Ľ –ł—Ö –ļ–ĺ–ī —á—É—ā—Ć –Ņ–ĺ–≤–Ĺ–ł–ľ–į—ā–Ķ–Ľ—Ć–Ĺ–Ķ–Ķ.[code]address opcode label comment

001000 5715C INNER n push n push 1000 0 DO

001001 003E8 1000

001002 00000 0

001003 57D58 IN1 n drop n pop 34 DROP

001004 00022 34

001005 00001 1

001006 BE37B + pop over over INC loop counter

001007 A080A xor T0 IN2 COMPARE

001008 FF39E drop push push nop

00100A FFFFE IN2 drop drop drop ; FINISH

00100B 5715C BENCH n push n push 1000 0 DO

00100C 003E8 1000

00100D 00000 0

00100E 20000 BE1 call INNER

00100F 563DE n pop nop nop

001010 00001 1

001011 BE37B + pop over over INC counter

001012 A0815 xor T0 BE2 COMPARE

001013 FF39E drop push push nop

001014 00003 jmp BE1 LOOP

001015 FFFBA BE2 drop drop drop n FINISH

001016 00007 7

001017 57020 n push ; long call and return

001018 03987 lit' EMIT[/code]–Ę–į–ľ –ľ–Ĺ–ĺ–≥–ĺ –ĺ–Ņ–Ķ—á–į—ā–ĺ–ļ, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –ĺ—ā—Ā—É—ā—Ā—ā–≤—É–Ķ—ā —Ā—ā—Ä–ĺ–ļ–į —Ā –į–ī—Ä–Ķ—Ā–ĺ–ľ 001009 (—ā–į–ľ –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ī—č—ā—Ć jmp IN1), –Ņ–ĺ –į–ī—Ä–Ķ—Ā—É 001014 –į–ī—Ä–Ķ—Ā –Ņ—Ä—č–∂–ļ–į –Ĺ–Ķ–Ņ—Ä–į–≤–ł–Ľ—Ć–Ĺ—č–Ļ (–ī–ĺ–Ľ–∂–Ķ–Ĺ –Ī—č—ā—Ć –Ņ—Ä—č–∂–ĺ–ļ –Ņ–ĺ –į–ī—Ä–Ķ—Ā—É XXXE, –į –Ĺ–Ķ XXX3, –≤–ł–ī–ł–ľ–ĺ, –Ĺ–Ķ–Ņ—Ä–į–≤–ł–Ľ—Ć–Ĺ–ĺ —Ä–į—Ā–Ņ–ĺ–∑–Ĺ–į–Ľ–ĺ—Ā—Ć –Ņ—Ä–ł —Ā–ļ–į–Ĺ–ł—Ä–ĺ–≤–į–Ĺ–ł–ł :) ), –ī–į –ł —Ą–ĺ—Ä–ľ–į—ā –ļ–ĺ–ľ–į–Ĺ–ī—č –≤—č–∑—č–≤–į–Ķ—ā –Ĺ–Ķ–ļ–ĺ—ā–ĺ—Ä—č–Ķ —Ā–ĺ–ľ–Ĺ–Ķ–Ĺ–ł—Ź. –Ě–į –≥–Ľ–į–∑ —ā–į–ľ –≤–ĺ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–Ķ–ľ —Ü–ł–ļ–Ľ–Ķ 15-20 –ļ–ĺ–ľ–į–Ĺ–ī, –Ĺ–ĺ —Ā–Ľ–ĺ–∂–Ĺ–ĺ –≤ —ā–į–ļ–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ –ĺ—Ü–Ķ–Ĺ–ł–≤–į—ā—Ć, –Ķ—Ā–Ľ–ł –Ĺ–Ķ –∑–Ĺ–į—ā—Ć, —Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —ā–į–ļ—ā–ĺ–≤ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź –ļ–į–∂–ī–į—Ź –ļ–ĺ–ľ–į–Ĺ–ī–į, –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –Ľ–ł –ĺ–Ĺ–ł –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ –ł —ā.–ī. –° –ī—Ä—É–≥–ĺ–Ļ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č —É –Ĺ–į—Ā –Ķ—Ā—ā—Ć —ā–į–ļ—ā–ĺ–≤–į—Ź —á–į—Ā—ā–ĺ—ā–į –ł –≤—Ä–Ķ–ľ—Ź –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł—Ź –ľ–ł–Ľ–Ľ–ł–ĺ–Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł–Ļ. –°–ľ–Ķ–Ľ–ĺ –Ņ–Ķ—Ä–Ķ–ľ–Ĺ–ĺ–∂–į–Ķ–ľ –ĺ–ī–Ĺ–ĺ –Ĺ–į –ī—Ä—É–≥–ĺ–Ķ - –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–ĺ —ā–į–ļ—ā–ĺ–≤ –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –≤–ĺ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–Ķ–ľ —Ü–ł–ļ–Ľ–Ķ: 200*0.17=34 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é —Ü–ł–ļ–Ľ–į –≤ INNER. –Ē–Ľ—Ź —Ā—Ä–į–≤–Ĺ–Ķ–Ĺ–ł—Ź 68040 –ł R4000 —ā—Ä–į—ā—Ź—ā –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –ī–ĺ—Ā—ā–ĺ–Ļ–Ĺ—č–Ķ 9 –ł 12 —ā–į–ļ—ā–ĺ–≤ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, –ī–į –ī–į–∂–Ķ 68030 —Ā –Ķ–≥–ĺ 18 —ā–į–ļ—ā–į–ľ–ł –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –Ĺ–Ķ —ā–į–ļ —É–∂ –ł –Ņ–Ľ–ĺ—Ö.

–°–ĺ–∑–ī–į—ā–Ķ–Ľ–ł F21 –Ņ—č—ā—é—ā—Ā—Ź –≤—č–Ļ—ā–ł –ł–∑ –Ņ–ĺ–Ľ–ĺ–∂–Ķ–Ĺ–ł—Ź –ł —Ä–į–∑–≤–ĺ—Ä–į—á–ł–≤–į—é—ā –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ļ —Ü–ł–ļ–Ľ, —É–Ī–ł—Ä–į—Ź —ā–Ķ–ľ —Ā–į–ľ—č–ľ –Ĺ–į–ļ–Ľ–į–ī–Ĺ—č–Ķ —Ä–į—Ā—Ö–ĺ–ī—č –Ĺ–į –ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—é —Ü–ł–ļ–Ľ–į, –≤ —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–Ķ –≤ –ĺ–Ī—Č–Ķ–ľ-—ā–ĺ –Ņ—Ä–ĺ—Ā—ā–ĺ–Ļ –ļ–ĺ–ī –∂–ł—Ä–Ķ–Ķ—ā –į–∂ –ī–ĺ 400 –Ī–į–Ļ—ā, –Ĺ–ĺ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–ĺ —ā–į–ļ—ā–ĺ–≤ –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é —É–ľ–Ķ–Ĺ—Ć—ą–į–Ķ—ā—Ā—Ź –≤—Ā–Ķ–≥–ĺ –Ľ–ł—ą—Ć –ī–ĺ 15. –ė –Ľ–ł—ą—Ć –ļ–ĺ–≥–ī–į –ĺ–Ĺ–ł –∑–į–ī–Ķ–Ļ—Ā—ā–≤—É—é—ā –≤–ľ–Ķ—Ā—ā–ĺ —á–Ķ—Ā—ā–Ĺ–ĺ–≥–ĺ –Ľ–ł—ā–Ķ—Ä–į–Ľ–į —Ā–≤–ĺ–Ļ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ļ —Ä–Ķ–≥–ł—Ā—ā—Ä –ź (–≤—Ä—É—á–Ĺ—É—é –ł–Ľ–ł –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–į–ľ —Ā–ĺ–ĺ–Ī—Ä–į–∑–ł–Ľ?), —ā–ĺ –Ņ–ĺ–Ľ—É—á–į—é—ā –ļ–ĺ—Ā–ľ–ł—á–Ķ—Ā–ļ–ł–Ķ 2 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é. :)

–ź —É –ľ–Ķ–Ĺ—Ź, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –≤ –Ī–į–∑–ĺ–≤–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ —Ā 6-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł –Ľ–ł—ā–Ķ—Ä–į–Ľ –≤–Ķ—Ā–ł—ā 2 –ļ–ĺ–ľ–į–Ĺ–ī—č (–ł —ā–į–ļ—ā–į), –Ķ—Č–Ķ —ā–į–ļ—ā –Ĺ–į drop, –Ĺ—É –ł –Ķ—Č–Ķ –ĺ–ī–ł–Ĺ –Ĺ–į loop. –í —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–Ķ –ł—ā–Ķ—Ä–į—Ü–ł—Ź –≤–Ķ—Ā–ł—ā 3 –Ī–į–Ļ—ā–į –ł –ī–Ľ–ł—ā—Ā—Ź 4 —ā–į–ļ—ā–į. –ź –≤ –Ņ—Ä–ĺ–ī–≤–ł–Ĺ—É—ā–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ (4- –ł 6-–Ī–ł—ā–Ĺ–ĺ–ľ) –≤—Ā–Ķ–≥–ĺ –ī–≤–į —ā–į–ļ—ā–į: –Ņ–Ķ—Ä–≤—č–Ļ –Ĺ–į 34+drop, –į –≤—ā–ĺ—Ä–ĺ–Ļ –Ĺ–į loop. –ü—Ä–ł –∂–Ķ–Ľ–į–Ĺ–ł–ł, –Ĺ–į–≤–Ķ—Ä–Ĺ–ĺ–Ķ, –ľ–ĺ–∂–Ĺ–ĺ –ł –≤ –ĺ–ī–ł–Ĺ —ā–į–ļ—ā —É–Ľ–ĺ–∂–ł—ā—Ć—Ā—Ź.

–ė –ī–į, –ļ–ĺ–ľ–į–Ĺ–ī—č –ī–Ľ—Ź —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –į–Ņ–Ņ–į—Ä–į—ā–Ĺ—č—Ö —Ü–ł–ļ–Ľ–ĺ–≤ - —ć—ā–ĺ (—Ā –ĺ–≥–ĺ–≤–ĺ—Ä–ļ–į–ľ–ł) —É—Ā–Ľ–ĺ–≤–Ĺ—č–Ķ call –ł ret. –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, while –ł do –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –ľ–ĺ–∂–Ĺ–ĺ –ĺ–Ī–ĺ–∑–≤–į—ā—Ć —É—Ā–Ľ–ĺ–≤–Ĺ—č–ľ call, –į repeat –ł loop - —É—Ā–Ľ–ĺ–≤–Ĺ—č–ľ–ł ret. –†–į–∑–Ĺ–ł—Ü–į –Ľ–ł—ą—Ć –≤ —ā–ĺ–ľ, —á—ā–ĺ –ĺ–ī–Ĺ–ł –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—é—ā –ł –ľ–Ķ–Ĺ—Ź—é—ā —Ā—á–Ķ—ā—á–ł–ļ —Ü–ł–ļ–Ľ–į, –į –ī—Ä—É–≥–ł–Ķ –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—é—ā —É—Ā–Ľ–ĺ–≤–ł–Ķ. –£—Ā–Ľ–ĺ–≤–Ĺ—č–ľ call –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ –Ņ–ĺ–Ľ–Ĺ—č–Ļ –Ľ–ł—ā–Ķ—Ä–į–Ľ (–į–ī—Ä–Ķ—Ā, –Ņ–ĺ –ļ–ĺ—ā–ĺ—Ä–ĺ–ľ—É –Ņ—Ä—č–≥–į—ā—Ć –Ņ—Ä–ł –Ĺ–Ķ–≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–ł —É—Ā–Ľ–ĺ–≤–ł—Ź), –Ĺ–ĺ –ĺ–Ĺ–ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –Ľ–ł—ą—Ć —Ä–į–∑ –≤ –ļ–į—á–Ķ—Ā—ā–≤–Ķ –Ņ—Ä–ĺ–Ľ–ĺ–≥–į –Ņ–Ķ—Ä–Ķ–ī –≤—Ö–ĺ–ī–ĺ–ľ –≤ —ā–Ķ–Ľ–ĺ —Ü–ł–ļ–Ľ–į, –į —É—Ā–Ľ–ĺ–≤–Ĺ—č–Ķ ret –Ľ–ł—ā–Ķ—Ä–į–Ľ–ĺ–≤ –Ĺ–Ķ —ā—Ä–Ķ–Ī—É—é—ā (–į–ī—Ä–Ķ—Ā –Ĺ–į—á–į–Ľ–į —Ü–ł–ļ–Ľ–į –Ī–Ķ—Ä—É—ā –ł–∑ —Ā—ā–Ķ–ļ–į –≤–ĺ–∑–≤—Ä–į—ā–ĺ–≤) –ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –∑–į —ā–į–ļ—ā.

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –ß—ā –ľ–į—Ä 21, 2024 01:25 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

|

–í —Ā–ł—Ā—ā–Ķ–ľ–Ķ –ļ–ĺ–ľ–į–Ĺ–ī –ľ–ĺ–∂–Ĺ–ĺ –ī–Ķ–Ľ–į—ā—Ć —Ā–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ—č–Ķ –Ņ–ĺ–Ľ—Ź, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –Ī—É–ī—É—ā –ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —Ä–į—Ā—á–Ķ—ā–į–ľ–ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī. –õ–ł—ā–Ķ—Ä–į–Ľ –≤ —ā–į–ļ—É—é –ļ–ĺ–ľ–į–Ĺ–ī—É —ā—Ä—É–ī–Ĺ–ĺ –ī–ĺ–Ī–į–≤–ł—ā—Ć, –į RET –ł–Ľ–ł LOOP –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –ľ–ĺ–∂–Ĺ–ĺ. –Ě–ĺ —ć—ā–ĺ —É–∂–Ķ –Ņ–ĺ–Ľ—É—á–ł—ā—Ā—Ź —É–Ņ—Ä–į–∂–Ĺ–Ķ–Ĺ–ł–Ķ "—Ä–į—Ā—Ā—ā–į–≤—Ć—ā–Ķ –Ņ–ĺ–Ľ—Ź –ļ–ĺ–ľ–į–Ĺ–ī—č, —á—ā–ĺ–Ī—č –Ī—č–Ľ–ĺ –ł –Ņ–ĺ–Ľ–Ķ–∑–Ĺ–ĺ, –ł –Ĺ–Ķ —Ā–Ľ–ł—ą–ļ–ĺ–ľ –≥—Ä–ĺ–ľ–ĺ–∑–ī–ļ–ĺ". –í —ā–Ķ—Ā—ā–į—Ö –Ņ–ĺ–Ĺ—Ź—ā–Ĺ–ĺ, —á—ā–ĺ –Ņ–ĺ —Ā—É—ā–ł —Ä–į–Ī–ĺ—ā–į–Ķ—ā —ā–ĺ–Ľ—Ć–ļ–ĺ —ā–Ķ–Ľ–ĺ –≤–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ–ĺ–≥–ĺ —Ü–ł–ļ–Ľ–į, –į –Ĺ–į–ļ–Ľ–į–ī–Ĺ—č–Ķ —Ä–į—Ā—Ö–ĺ–ī—č –ł–ī—É—ā –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ —Ā –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–Ķ–ľ —Ā—ā–Ķ–ļ–ĺ–≤—č—Ö –ľ–į–Ĺ–ł–Ņ—É–Ľ—Ź—Ü–ł–Ļ. –Ě—É, –ĺ–Ĺ–ĺ —ā–ĺ–∂–Ķ –ł–ľ–Ķ–Ķ—ā –Ņ—Ä–į–≤–ĺ –Ĺ–į –∂–ł–∑–Ĺ—Ć.

–í —Ā–ł—Ā—ā–Ķ–ľ–Ķ –ļ–ĺ–ľ–į–Ĺ–ī –ľ–ĺ–∂–Ĺ–ĺ –ī–Ķ–Ľ–į—ā—Ć —Ā–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ—č–Ķ –Ņ–ĺ–Ľ—Ź, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –Ī—É–ī—É—ā –ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —Ä–į—Ā—á–Ķ—ā–į–ľ–ł –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī. –õ–ł—ā–Ķ—Ä–į–Ľ –≤ —ā–į–ļ—É—é –ļ–ĺ–ľ–į–Ĺ–ī—É —ā—Ä—É–ī–Ĺ–ĺ –ī–ĺ–Ī–į–≤–ł—ā—Ć, –į RET –ł–Ľ–ł LOOP –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –ľ–ĺ–∂–Ĺ–ĺ. –Ě–ĺ —ć—ā–ĺ —É–∂–Ķ –Ņ–ĺ–Ľ—É—á–ł—ā—Ā—Ź —É–Ņ—Ä–į–∂–Ĺ–Ķ–Ĺ–ł–Ķ "—Ä–į—Ā—Ā—ā–į–≤—Ć—ā–Ķ –Ņ–ĺ–Ľ—Ź –ļ–ĺ–ľ–į–Ĺ–ī—č, —á—ā–ĺ–Ī—č –Ī—č–Ľ–ĺ –ł –Ņ–ĺ–Ľ–Ķ–∑–Ĺ–ĺ, –ł –Ĺ–Ķ —Ā–Ľ–ł—ą–ļ–ĺ–ľ –≥—Ä–ĺ–ľ–ĺ–∑–ī–ļ–ĺ". –í —ā–Ķ—Ā—ā–į—Ö –Ņ–ĺ–Ĺ—Ź—ā–Ĺ–ĺ, —á—ā–ĺ –Ņ–ĺ —Ā—É—ā–ł —Ä–į–Ī–ĺ—ā–į–Ķ—ā —ā–ĺ–Ľ—Ć–ļ–ĺ —ā–Ķ–Ľ–ĺ –≤–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ–ĺ–≥–ĺ —Ü–ł–ļ–Ľ–į, –į –Ĺ–į–ļ–Ľ–į–ī–Ĺ—č–Ķ —Ä–į—Ā—Ö–ĺ–ī—č –ł–ī—É—ā –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ —Ā –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–Ķ–ľ —Ā—ā–Ķ–ļ–ĺ–≤—č—Ö –ľ–į–Ĺ–ł–Ņ—É–Ľ—Ź—Ü–ł–Ļ. –Ě—É, –ĺ–Ĺ–ĺ —ā–ĺ–∂–Ķ –ł–ľ–Ķ–Ķ—ā –Ņ—Ä–į–≤–ĺ –Ĺ–į –∂–ł–∑–Ĺ—Ć.

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°—Ä –ľ–į—Ä 20, 2024 17:38 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

–Ě–Ķ–ľ–Ĺ–ĺ–≥–ĺ —Ä–į—Ā—ą–Ķ–≤–Ķ–Ľ–ł—ā—Ć —ā–Ķ–ľ—É. –ü–ĺ–Ņ–į–Ľ–į—Ā—Ć —ā—É—ā –Ĺ–Ķ–ī–į–≤–Ĺ–ĺ –ī—Ä–Ķ–≤–Ĺ—Ź—Ź —Ā—ā–į—ā—Ć—Ź https://www.ultratechnology.com/forml93.html–Ę–į–ľ –≤—Ā—Ď –Ņ–ĺ–≤–Ķ—Ā—ā–≤–ĺ–≤–į–Ĺ–ł–Ķ –≤–ĺ–ļ—Ä—É–≥ –ī–į –ĺ–ļ–ĺ–Ľ–ĺ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į F21. –ė –≤ —á–ł—Ā–Ľ–Ķ –Ņ—Ä–ĺ—á–Ķ–≥–ĺ –Ņ—Ä–ł–≤–Ķ–ī–Ķ–Ĺ –Ņ—Ä–ĺ—Ā—ā–Ķ–Ĺ—Ć–ļ–ł–Ļ —ā–Ķ—Ā—ā –ö–ĺ–ī: : INNER 1000 0 DO 34 DROP LOOP :

: BENCH 1000 0 DO INNER LOOP 7 EMIT ; –≠—ā–ĺ—ā —ā–Ķ—Ā—ā –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź –Ĺ–į —Ä–į–∑–Ĺ—č—Ö —Ą–ĺ—Ä—ā–į—Ö –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į—Ö, –Ņ–ĺ–ļ–į–∑–į—ā–Ķ–Ľ–ł (–Ņ–ĺ—á–Ķ–ľ—É-—ā–ĺ –į–Ī—Ā–ĺ–Ľ—é—ā–Ĺ—č–Ķ) –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł —Ā—Ä–į–≤–Ĺ–ł–≤–į—é—ā—Ā—Ź –ł –ī–Ķ–Ľ–į–Ķ—ā—Ā—Ź –≤—č–≤–ĺ–ī –ĺ –ļ—Ä—É—ā–ĺ—Ā—ā–ł F21 –ł —É—Č–Ķ—Ä–Ī–Ĺ–ĺ—Ā—ā–ł –Ņ—Ä–ĺ—á–ł—Ö –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–≤.  –Ę.–ļ. –ľ–ĺ–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —Ā 6-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł —ā–ĺ–∂–Ķ –∑–į—Ä–į–Ī–ĺ—ā–į–Ľ, —ā–ĺ —Ä–Ķ—ą–ł–Ľ –ł—Ā–Ņ—č—ā–į—ā—Ć –Ķ–≥–ĺ (–į –∑–į–ĺ–ī–Ĺ–ĺ –ł –Ņ—Ä–Ķ–ī—č–ī—É—Č–ł–Ķ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł) –Ņ—Ä–ł –Ņ–ĺ–ľ–ĺ—Č–ł —ć—ā–ĺ–≥–ĺ —ā–Ķ—Ā—ā–į. –Ę–į–Ī–Ľ–ł—Ü–į —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–ĺ–≤ —ā–į–ľ —ā–į–ļ–į—Ź: –ö–ĺ–ī: PROCESSOR CLOCK FORTH-COMPILER OPTION SECONDS

VAX 6620 FIG 8080 (EMULATION) 15.32

H8 10 eForth 15.0

68000 7 7.6

80386 33 HS/FORTH 6.1

MuP21 100 MuP21 eForth 2.02 DRAM 3.3

80486 33 F83 in "C" 3.0

80386 33 FPC 2.8

68040 25 Yerk 2.7

F21 200 MuP21 eForth 2.02 DRAM 2.6

80386 33 TCOM (FPC) 1.7

80386 33 HS/FORTH w/optimization 1.6 no 34 DROP

80386 33 TCOM (FPC) 0.99 no 7 EMIT

HP-PA Forth in "C" 0.75

68030 25 0.75

F21 200 F21 eForth STC 2.03 DRAM 0.7

R3000 33 RISC pFORTH INDIGO 0.66

F21 200 F21 eForth STC 2.04 DRAM 0.65

MuP21 100 fforth DRAM 0.45

68040 25 0.35

R3000 66 RISC pFORTH INDIGO 0.33

MuP21 100 fforth SRAM 0.3

F21 200 fforth DRAM 0.25

R4000 50 RISC pFORTH CRIMSON 0.24

80486 33 ForthCMP 0.21 no 34 DROP

MuP21 100 fforth **1 DRAM 0.19

F21 200 fforth SRAM 0.17

MuP21 100 fforth **1 SRAM 0.14

F21 200 fforth **1 DRAM 0.137

R4000 100 RISC pFORTH CRIMSON 0.12

F21 200 fforth **1 SRAM 0.077

MuP21 100 fforth **2 DRAM 0.027

MuP21 100 fforth **2 SRAM 0.02

F21 200 fforth **2 DRAM 0.02

F21 200 fforth **2 SRAM 0.01 –ź –ī–Ľ—Ź –ľ–ĺ–ł—Ö –Ņ–ĺ–ī–ĺ–Ņ–Ķ—á–Ĺ—č—Ö –Ņ–ĺ–Ľ—É—á–ł–Ľ–ł—Ā—Ć —ā–į–ļ–ł–Ķ —Ü–ł—Ą—Ä—č: –ö–ĺ–ī: f41/f42 20 uforth 1.09 22 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é

f43/f44 20 uforth 1.00 20 —ā–į–ļ—ā–ĺ–≤ –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é

f61 20 uforth 0.199 4 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –ė –Ņ–ĺ–Ľ—É—á–į–Ķ—ā—Ā—Ź, —á—ā–ĺ –Ķ—Ā–Ľ–ł –Ĺ–Ķ —Ä–į—Ā—Ā–ľ–į—ā—Ä–ł–≤–į—ā—Ć —Ä–į–∑–Ĺ—č–Ķ —É—Ö–ł—Č—Ä–Ķ–Ĺ–ł—Ź –≤—Ä–ĺ–ī–Ķ —Ä–į–∑–≤–ĺ—Ä–į—á–ł–≤–į–Ĺ–ł—Ź —Ü–ł–ļ–Ľ–į –ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź —Ä–Ķ–≥–ł—Ā—ā—Ä–į –≤–ľ–Ķ—Ā—ā–ĺ —á–Ķ—Ā—ā–Ĺ–ĺ–Ļ –∑–į–Ņ–ł—Ā–ł —á–ł—Ā–Ľ–į –≤ —Ā—ā–Ķ–ļ, —ā–ĺ, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, f61 –Ņ—Ä–į–ļ—ā–ł—á–Ķ—Ā–ļ–ł –Ĺ–Ķ —É—Ā—ā—É–Ņ–į–Ķ—ā –Ņ–ĺ –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É F21 –ī–į–∂–Ķ –Ĺ–Ķ—Ā–ľ–ĺ—ā—Ä—Ź –Ĺ–į 10-–ļ—Ä–į—ā–Ĺ–ĺ –ľ–Ķ–Ĺ—Ć—ą—É—é —ā–į–ļ—ā–ĺ–≤—É—é —á–į—Ā—ā–ĺ—ā—É (20 –Ņ—Ä–ĺ—ā–ł–≤ 200–ú–ď—Ü), –ī–į –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł —É—Ā—ā—É–Ņ–į—é—ā –≤—Ā–Ķ–≥–ĺ –Ľ–ł—ą—Ć –≤ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —Ä–į–∑.  –ö—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ, —Ā–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ–ĺ –ĺ–Ī—É—á–Ķ–Ĺ–Ĺ—č–Ķ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č f4/f6, —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ—č–Ķ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī –∑–į —ā–į–ļ—ā, –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā —ā–ĺ—ā –∂–Ķ —Ā–į–ľ—č–Ļ –Ĺ–Ķ–ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ī, –∑–į—ā—Ä–į—á–ł–≤–į—Ź –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –≤—Ā–Ķ–≥–ĺ –Ľ–ł—ą—Ć 2 —ā–į–ļ—ā–į  –Ę.–Ķ. –Ķ—Ā–Ľ–ł –Ņ—Ä–ł–≤–Ķ—Ā—ā–ł —á–į—Ā—ā–ĺ—ā—č –ļ –ĺ–ī–Ĺ–ĺ–ľ—É –∑–Ĺ–į–ľ–Ķ–Ĺ–į—ā–Ķ–Ľ—é, —ā–ĺ –Ī—É–ī–Ķ—ā —Ä–ĺ–≤–Ĺ–ĺ —ā–į–ļ–ĺ–Ļ –∂–Ķ —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā, –ļ–į–ļ –ł —É F21 —Ā —Ä–į–∑–≤–Ķ—Ä–Ĺ—É—ā—č–ľ–ł —Ü–ł–ļ–Ľ–į–ľ–ł –ł –∑–į–ī–Ķ–Ļ—Ā—ā–≤–ĺ–≤–į–Ĺ–Ĺ—č–ľ —Ä–Ķ–≥–ł—Ā—ā—Ä–ĺ–ľ –ź, —ā.–Ķ. —ā–Ķ –∂–Ķ —Ā–į–ľ—č–Ķ 2 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é. –Ē—Ä—É–≥–ł–ľ–ł —Ā–Ľ–ĺ–≤–į–ľ–ł, F21 –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ī, –į f4/f6 - –ĺ–Ī—č—á–Ĺ—č–Ļ –Ĺ–Ķ–ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ, –Ĺ–ĺ –Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā—Ć –ĺ–ī–ł–Ĺ–į–ļ–ĺ–≤–į—Ź. –ē—Č–Ķ –∑–į–Ī–į–≤–Ĺ–ĺ, —á—ā–ĺ –Ķ—Ā–Ľ–ł –≤—č—Ä–ĺ–≤–Ĺ—Ź—ā—Ć —á–į—Ā—ā–ĺ—ā—č, —ā–ĺ R4000 (MIPS?), 68040, –į –ľ–ĺ–∂–Ķ—ā –ł –Ķ—Č–Ķ –ļ–į–ļ–ł–Ķ-—ā–ĺ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —Ā –ļ–į–ļ–ł–ľ-—ā–ĺ –Ľ–Ķ–≤—č–ľ —Ą–ĺ—Ä—ā–ĺ–ľ –ĺ–ļ–į–∂—É—ā—Ā—Ź –Ī—č—Ā—ā—Ä–Ķ–Ķ, —á–Ķ–ľ F21 —Ā —Ä–ĺ–ī–Ĺ—č–ľ —Ą–ĺ—Ä—ā–ĺ–ľ  –Ě–Ķ–ľ–Ĺ–ĺ–≥–ĺ —Ä–į—Ā—ą–Ķ–≤–Ķ–Ľ–ł—ā—Ć —ā–Ķ–ľ—É.

–ü–ĺ–Ņ–į–Ľ–į—Ā—Ć —ā—É—ā –Ĺ–Ķ–ī–į–≤–Ĺ–ĺ –ī—Ä–Ķ–≤–Ĺ—Ź—Ź —Ā—ā–į—ā—Ć—Ź [url]https://www.ultratechnology.com/forml93.html[/url]

–Ę–į–ľ –≤—Ā—Ď –Ņ–ĺ–≤–Ķ—Ā—ā–≤–ĺ–≤–į–Ĺ–ł–Ķ –≤–ĺ–ļ—Ä—É–≥ –ī–į –ĺ–ļ–ĺ–Ľ–ĺ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į F21. –ė –≤ —á–ł—Ā–Ľ–Ķ –Ņ—Ä–ĺ—á–Ķ–≥–ĺ –Ņ—Ä–ł–≤–Ķ–ī–Ķ–Ĺ –Ņ—Ä–ĺ—Ā—ā–Ķ–Ĺ—Ć–ļ–ł–Ļ —ā–Ķ—Ā—ā[code]: INNER 1000 0 DO 34 DROP LOOP :

: BENCH 1000 0 DO INNER LOOP 7 EMIT ;[/code]–≠—ā–ĺ—ā —ā–Ķ—Ā—ā –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź –Ĺ–į —Ä–į–∑–Ĺ—č—Ö —Ą–ĺ—Ä—ā–į—Ö –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į—Ö, –Ņ–ĺ–ļ–į–∑–į—ā–Ķ–Ľ–ł (–Ņ–ĺ—á–Ķ–ľ—É-—ā–ĺ –į–Ī—Ā–ĺ–Ľ—é—ā–Ĺ—č–Ķ) –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł —Ā—Ä–į–≤–Ĺ–ł–≤–į—é—ā—Ā—Ź –ł –ī–Ķ–Ľ–į–Ķ—ā—Ā—Ź –≤—č–≤–ĺ–ī –ĺ –ļ—Ä—É—ā–ĺ—Ā—ā–ł F21 –ł —É—Č–Ķ—Ä–Ī–Ĺ–ĺ—Ā—ā–ł –Ņ—Ä–ĺ—á–ł—Ö –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–≤. :) –Ę.–ļ. –ľ–ĺ–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —Ā 6-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł —ā–ĺ–∂–Ķ –∑–į—Ä–į–Ī–ĺ—ā–į–Ľ, —ā–ĺ —Ä–Ķ—ą–ł–Ľ –ł—Ā–Ņ—č—ā–į—ā—Ć –Ķ–≥–ĺ (–į –∑–į–ĺ–ī–Ĺ–ĺ –ł –Ņ—Ä–Ķ–ī—č–ī—É—Č–ł–Ķ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł) –Ņ—Ä–ł –Ņ–ĺ–ľ–ĺ—Č–ł —ć—ā–ĺ–≥–ĺ —ā–Ķ—Ā—ā–į.

–Ę–į–Ī–Ľ–ł—Ü–į —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–ĺ–≤ —ā–į–ľ —ā–į–ļ–į—Ź:[code]PROCESSOR CLOCK FORTH-COMPILER OPTION SECONDS

VAX 6620 FIG 8080 (EMULATION) 15.32

H8 10 eForth 15.0

68000 7 7.6

80386 33 HS/FORTH 6.1

MuP21 100 MuP21 eForth 2.02 DRAM 3.3

80486 33 F83 in "C" 3.0

80386 33 FPC 2.8

68040 25 Yerk 2.7

F21 200 MuP21 eForth 2.02 DRAM 2.6

80386 33 TCOM (FPC) 1.7

80386 33 HS/FORTH w/optimization 1.6 no 34 DROP

80386 33 TCOM (FPC) 0.99 no 7 EMIT

HP-PA Forth in "C" 0.75

68030 25 0.75

F21 200 F21 eForth STC 2.03 DRAM 0.7

R3000 33 RISC pFORTH INDIGO 0.66

F21 200 F21 eForth STC 2.04 DRAM 0.65

MuP21 100 fforth DRAM 0.45

68040 25 0.35

R3000 66 RISC pFORTH INDIGO 0.33

MuP21 100 fforth SRAM 0.3

F21 200 fforth DRAM 0.25

R4000 50 RISC pFORTH CRIMSON 0.24

80486 33 ForthCMP 0.21 no 34 DROP

MuP21 100 fforth **1 DRAM 0.19

F21 200 fforth SRAM 0.17

MuP21 100 fforth **1 SRAM 0.14

F21 200 fforth **1 DRAM 0.137

R4000 100 RISC pFORTH CRIMSON 0.12

F21 200 fforth **1 SRAM 0.077

MuP21 100 fforth **2 DRAM 0.027

MuP21 100 fforth **2 SRAM 0.02

F21 200 fforth **2 DRAM 0.02

F21 200 fforth **2 SRAM 0.01[/code]–ź –ī–Ľ—Ź –ľ–ĺ–ł—Ö –Ņ–ĺ–ī–ĺ–Ņ–Ķ—á–Ĺ—č—Ö –Ņ–ĺ–Ľ—É—á–ł–Ľ–ł—Ā—Ć —ā–į–ļ–ł–Ķ —Ü–ł—Ą—Ä—č:[code]f41/f42 20 uforth 1.09 22 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é

f43/f44 20 uforth 1.00 20 —ā–į–ļ—ā–ĺ–≤ –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é

f61 20 uforth 0.199 4 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é[/code]

–ė –Ņ–ĺ–Ľ—É—á–į–Ķ—ā—Ā—Ź, —á—ā–ĺ –Ķ—Ā–Ľ–ł –Ĺ–Ķ —Ä–į—Ā—Ā–ľ–į—ā—Ä–ł–≤–į—ā—Ć —Ä–į–∑–Ĺ—č–Ķ —É—Ö–ł—Č—Ä–Ķ–Ĺ–ł—Ź –≤—Ä–ĺ–ī–Ķ —Ä–į–∑–≤–ĺ—Ä–į—á–ł–≤–į–Ĺ–ł—Ź —Ü–ł–ļ–Ľ–į –ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź —Ä–Ķ–≥–ł—Ā—ā—Ä–į –≤–ľ–Ķ—Ā—ā–ĺ —á–Ķ—Ā—ā–Ĺ–ĺ–Ļ –∑–į–Ņ–ł—Ā–ł —á–ł—Ā–Ľ–į –≤ —Ā—ā–Ķ–ļ, —ā–ĺ, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, f61 –Ņ—Ä–į–ļ—ā–ł—á–Ķ—Ā–ļ–ł –Ĺ–Ķ —É—Ā—ā—É–Ņ–į–Ķ—ā –Ņ–ĺ –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É F21 –ī–į–∂–Ķ –Ĺ–Ķ—Ā–ľ–ĺ—ā—Ä—Ź –Ĺ–į 10-–ļ—Ä–į—ā–Ĺ–ĺ –ľ–Ķ–Ĺ—Ć—ą—É—é —ā–į–ļ—ā–ĺ–≤—É—é —á–į—Ā—ā–ĺ—ā—É (20 –Ņ—Ä–ĺ—ā–ł–≤ 200–ú–ď—Ü), –ī–į –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł —É—Ā—ā—É–Ņ–į—é—ā –≤—Ā–Ķ–≥–ĺ –Ľ–ł—ą—Ć –≤ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —Ä–į–∑. :) –ö—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ, —Ā–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ–ĺ –ĺ–Ī—É—á–Ķ–Ĺ–Ĺ—č–Ķ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č f4/f6, —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ—č–Ķ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī –∑–į —ā–į–ļ—ā, –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā —ā–ĺ—ā –∂–Ķ —Ā–į–ľ—č–Ļ –Ĺ–Ķ–ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ī, –∑–į—ā—Ä–į—á–ł–≤–į—Ź –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é –≤—Ā–Ķ–≥–ĺ –Ľ–ł—ą—Ć 2 —ā–į–ļ—ā–į :) –Ę.–Ķ. –Ķ—Ā–Ľ–ł –Ņ—Ä–ł–≤–Ķ—Ā—ā–ł —á–į—Ā—ā–ĺ—ā—č –ļ –ĺ–ī–Ĺ–ĺ–ľ—É –∑–Ĺ–į–ľ–Ķ–Ĺ–į—ā–Ķ–Ľ—é, —ā–ĺ –Ī—É–ī–Ķ—ā —Ä–ĺ–≤–Ĺ–ĺ —ā–į–ļ–ĺ–Ļ –∂–Ķ —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā, –ļ–į–ļ –ł —É F21 —Ā —Ä–į–∑–≤–Ķ—Ä–Ĺ—É—ā—č–ľ–ł —Ü–ł–ļ–Ľ–į–ľ–ł –ł –∑–į–ī–Ķ–Ļ—Ā—ā–≤–ĺ–≤–į–Ĺ–Ĺ—č–ľ —Ä–Ķ–≥–ł—Ā—ā—Ä–ĺ–ľ –ź, —ā.–Ķ. —ā–Ķ –∂–Ķ —Ā–į–ľ—č–Ķ 2 —ā–į–ļ—ā–į –Ĺ–į –ł—ā–Ķ—Ä–į—Ü–ł—é. –Ē—Ä—É–≥–ł–ľ–ł —Ā–Ľ–ĺ–≤–į–ľ–ł, F21 –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ī, –į f4/f6 - –ĺ–Ī—č—á–Ĺ—č–Ļ –Ĺ–Ķ–ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ, –Ĺ–ĺ –Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā—Ć –ĺ–ī–ł–Ĺ–į–ļ–ĺ–≤–į—Ź. –ē—Č–Ķ –∑–į–Ī–į–≤–Ĺ–ĺ, —á—ā–ĺ –Ķ—Ā–Ľ–ł –≤—č—Ä–ĺ–≤–Ĺ—Ź—ā—Ć —á–į—Ā—ā–ĺ—ā—č, —ā–ĺ R4000 (MIPS?), 68040, –į –ľ–ĺ–∂–Ķ—ā –ł –Ķ—Č–Ķ –ļ–į–ļ–ł–Ķ-—ā–ĺ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —Ā –ļ–į–ļ–ł–ľ-—ā–ĺ –Ľ–Ķ–≤—č–ľ —Ą–ĺ—Ä—ā–ĺ–ľ –ĺ–ļ–į–∂—É—ā—Ā—Ź –Ī—č—Ā—ā—Ä–Ķ–Ķ, —á–Ķ–ľ F21 —Ā —Ä–ĺ–ī–Ĺ—č–ľ —Ą–ĺ—Ä—ā–ĺ–ľ :)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°—Ä –ľ–į—Ä 20, 2024 01:51 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

KPG –Ņ–ł—Ā–į–Ľ(–į): –ź, —á–Ķ–ľ "–Ņ–Ľ–ĺ—Ö" –≤–į—Ä–ł–į–Ĺ—ā –ł—Ā–Ņ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź –§–ĺ—Ä—ā –ī–Ľ—Ź –ī–Ľ—Ź —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–ł –°–ł?

–ú–ĺ–≥—É —Ā–ļ–ł–Ĺ—É—ā—Ć —Ā–≤–ĺ–Ļ –≤–į—Ä–ł–į–Ĺ—ā –Ņ—Ä–ĺ—ā–ĺ—ā–ł–Ņ–į LCC -> SPf4 (–ī–Ķ–Ľ–į–Ľ—Ā—Ź –Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ C2Forth on Mpe Ltd —Ā –ł—Ö —Ā–į–Ļ—ā–į)

–ł –≤–į—Ä–ł–į–Ĺ—ā –ĺ—ā –ú–ł—Ö–į–ł–Ľ–į. (–ĺ–Ĺ –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑–ĺ–≤—č–≤–į–Ľ LCC —Ą—Ä–ĺ–Ĺ—ā-end –≤ –ļ–ĺ–ī SPF4), —É –ľ–Ķ–Ĺ—Ź LCC –ĺ—ā –°–ł (—Ā–Ī–ĺ—Ä–ļ–į –Ĺ–į PellesC),

–į –Ī–ł–Ī–Ľ–ł–ĺ—ā–Ķ–ļ–ł (stdlib, stdio ...) —É–∂–Ķ –Ĺ–į SPF4 (—ā–ĺ–Ņ–ł–ļ –Ķ—Ā—ā—Ć –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ) –Ē–į —Ź –≤—Ä–ĺ–ī–Ķ –Ĺ–Ķ –≥–ĺ–≤–ĺ—Ä–ł–Ľ, —á—ā–ĺ "–Ņ–Ľ–ĺ—Ö"  –ė —ā–Ķ–ľ –Ĺ–Ķ –ľ–Ķ–Ĺ–Ķ–Ķ, –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä –°–ł –Ľ—É—á—ą–Ķ –Ņ–ł—Ā–į—ā—Ć –Ĺ–į –°–ł, –≤–Ķ–ī—Ć –Ņ—Ä–ĺ–≤–Ķ—Ä–ļ–į —Ā–į–ľ–ĺ–ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä—É–Ķ–ľ–ĺ—Ā—ā–ł - —ć—ā–ĺ –Ķ–ī–≤–į –Ľ–ł –Ĺ–Ķ –Ľ—É—á—ą–ł–Ļ —ā–Ķ—Ā—ā, –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—é—Č–ł–Ļ —Ä–į–Ī–ĺ—ā–ĺ—Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ–ĺ—Ā—ā—Ć. –ź –≤–ĺ –≤—ā–ĺ—Ä—č—Ö, "–ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł–Ķ –§–ĺ—Ä—ā –ī–Ľ—Ź —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–ł –°–ł" –į–≤—ā–ĺ–ľ–į—ā–ł—á–Ķ—Ā–ļ–ł –Ņ–ĺ–Ľ—É—á–ł—ā—Ā—Ź "–Ĺ–į —Ā–ī–į—á—É" (–≤—č—Ö–Ľ–ĺ–Ņ-—ā–ĺ –Ĺ–į –§–ĺ—Ä—ā–Ķ!  ) –Ņ–ĺ—Ā–Ľ–Ķ —ā–ĺ–≥–ĺ, –ļ–į–ļ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä –Ī—É–ī–Ķ—ā —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ķ–Ĺ –ļ–ĺ–ľ–Ņ–ł—Ä–ĺ–≤–į—ā—Ć —Ā–į–ľ —Ā–Ķ–Ī—Ź  –ü–ĺ–Ĺ—Ź—ā–Ĺ–ĺ, —á—ā–ĺ –ļ–ĺ–ī –Ķ—Č–Ķ –Ņ—Ä–ł–ī–Ķ—ā—Ā—Ź —ą–Ľ–ł—Ą–į–Ĺ—É—ā—Ć –Ĺ–į–Ņ–ł–Ľ—Ć–Ĺ–ł–ļ–ĺ–ľ, —á—ā–ĺ–Ī—č –ĺ–Ĺ —á–ł—ā–į–Ľ—Ā—Ź –ł –Ņ–ĺ–Ņ—Ä–ĺ—Č–Ķ –Ī—č–Ľ, –Ĺ–ĺ —ā–Ķ–ľ –Ĺ–Ķ –ľ–Ķ–Ĺ–Ķ–Ķ... –†–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –°–ł-–≤-–§–ĺ—Ä—ā –Ĺ–į –§–ĺ—Ä—ā–Ķ –Ī—č–Ľ–ĺ –Ī—č –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ĺ–ĺ –Ņ–ĺ—Ā–ľ–ĺ—ā—Ä–Ķ—ā—Ć, –∑–ī–Ķ—Ā—Ć –Ĺ–į —Ą–ĺ—Ä—É–ľ–Ķ –≤—Ä–ĺ–ī–Ķ –Ī—č–Ľ–į —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–į—Ź —ā–Ķ–ľ–į, –Ĺ–ĺ —Ā—Ā—č–Ľ–ļ–ł —ā–į–ľ –ī–į–≤–Ĺ–ĺ –Ņ—Ä–ĺ—ā—É—Ö–Ľ–ł. –ü—Ä–ĺ —Ā2forth –ĺ—ā mpe —Ź –≤—Ä–ĺ–ī–Ķ —á–ł—ā–į–Ľ –ļ–ĺ–≥–ī–į-—ā–ĺ –ī–į–≤–Ĺ–ĺ, —á—ā–ĺ-—ā–ĺ —ā–į–ļ–ĺ–Ķ –Ņ—Ä–ł–Ņ–ĺ–ľ–ł–Ĺ–į—é —Ā–ľ—É—ā–Ĺ–ĺ, —ā–į–ľ —É –Ĺ–ł—Ö –ļ–į–∂–ł—Ā—Ć –ī–į–∂–Ķ float –Ĺ–Ķ –∑–į–≤–Ķ–∑–Ľ–ł, –Ĺ–ĺ –ľ–ĺ–≥—É –ĺ—ą–ł–Ī–į—ā—Ć—Ā—Ź. –ė –ĺ—Ä–ł–≥–ł–Ĺ–į–Ľ—Ć–Ĺ—č–Ļ LCC –≤—Ä–ĺ–ī–Ķ —Ā–ľ–ĺ—ā—Ä–Ķ–Ľ, –ľ–Ĺ–Ķ –ĺ–Ĺ –Ņ–ĺ–ļ–į–∑–į–Ľ—Ā—Ź –ļ–į–ļ–ł–ľ-—ā–ĺ –≥—Ä–ĺ–ľ–ĺ–∑–ī–ļ–ł–ľ.  [quote="KPG"]–ź, —á–Ķ–ľ "–Ņ–Ľ–ĺ—Ö" –≤–į—Ä–ł–į–Ĺ—ā –ł—Ā–Ņ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź –§–ĺ—Ä—ā –ī–Ľ—Ź –ī–Ľ—Ź —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–ł –°–ł?

–ú–ĺ–≥—É —Ā–ļ–ł–Ĺ—É—ā—Ć —Ā–≤–ĺ–Ļ –≤–į—Ä–ł–į–Ĺ—ā –Ņ—Ä–ĺ—ā–ĺ—ā–ł–Ņ–į LCC -> SPf4 (–ī–Ķ–Ľ–į–Ľ—Ā—Ź –Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ C2Forth on Mpe Ltd —Ā –ł—Ö —Ā–į–Ļ—ā–į)

–ł –≤–į—Ä–ł–į–Ĺ—ā –ĺ—ā –ú–ł—Ö–į–ł–Ľ–į. (–ĺ–Ĺ –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑–ĺ–≤—č–≤–į–Ľ LCC —Ą—Ä–ĺ–Ĺ—ā-end –≤ –ļ–ĺ–ī SPF4), —É –ľ–Ķ–Ĺ—Ź LCC –ĺ—ā –°–ł (—Ā–Ī–ĺ—Ä–ļ–į –Ĺ–į PellesC),

–į –Ī–ł–Ī–Ľ–ł–ĺ—ā–Ķ–ļ–ł (stdlib, stdio ...) —É–∂–Ķ –Ĺ–į SPF4 (—ā–ĺ–Ņ–ł–ļ –Ķ—Ā—ā—Ć –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ)[/quote]–Ē–į —Ź –≤—Ä–ĺ–ī–Ķ –Ĺ–Ķ –≥–ĺ–≤–ĺ—Ä–ł–Ľ, —á—ā–ĺ "–Ņ–Ľ–ĺ—Ö" :) –ė —ā–Ķ–ľ –Ĺ–Ķ –ľ–Ķ–Ĺ–Ķ–Ķ, –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä –°–ł –Ľ—É—á—ą–Ķ –Ņ–ł—Ā–į—ā—Ć –Ĺ–į –°–ł, –≤–Ķ–ī—Ć –Ņ—Ä–ĺ–≤–Ķ—Ä–ļ–į —Ā–į–ľ–ĺ–ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä—É–Ķ–ľ–ĺ—Ā—ā–ł - —ć—ā–ĺ –Ķ–ī–≤–į –Ľ–ł –Ĺ–Ķ –Ľ—É—á—ą–ł–Ļ —ā–Ķ—Ā—ā, –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—é—Č–ł–Ļ —Ä–į–Ī–ĺ—ā–ĺ—Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ–ĺ—Ā—ā—Ć. –ź –≤–ĺ –≤—ā–ĺ—Ä—č—Ö, "–ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł–Ķ –§–ĺ—Ä—ā –ī–Ľ—Ź —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–ł –°–ł" –į–≤—ā–ĺ–ľ–į—ā–ł—á–Ķ—Ā–ļ–ł –Ņ–ĺ–Ľ—É—á–ł—ā—Ā—Ź "–Ĺ–į —Ā–ī–į—á—É" (–≤—č—Ö–Ľ–ĺ–Ņ-—ā–ĺ –Ĺ–į –§–ĺ—Ä—ā–Ķ! :) ) –Ņ–ĺ—Ā–Ľ–Ķ —ā–ĺ–≥–ĺ, –ļ–į–ļ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä –Ī—É–ī–Ķ—ā —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ķ–Ĺ –ļ–ĺ–ľ–Ņ–ł—Ä–ĺ–≤–į—ā—Ć —Ā–į–ľ —Ā–Ķ–Ī—Ź :) –ü–ĺ–Ĺ—Ź—ā–Ĺ–ĺ, —á—ā–ĺ –ļ–ĺ–ī –Ķ—Č–Ķ –Ņ—Ä–ł–ī–Ķ—ā—Ā—Ź —ą–Ľ–ł—Ą–į–Ĺ—É—ā—Ć –Ĺ–į–Ņ–ł–Ľ—Ć–Ĺ–ł–ļ–ĺ–ľ, —á—ā–ĺ–Ī—č –ĺ–Ĺ —á–ł—ā–į–Ľ—Ā—Ź –ł –Ņ–ĺ–Ņ—Ä–ĺ—Č–Ķ –Ī—č–Ľ, –Ĺ–ĺ —ā–Ķ–ľ –Ĺ–Ķ –ľ–Ķ–Ĺ–Ķ–Ķ...

–†–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –°–ł-–≤-–§–ĺ—Ä—ā –Ĺ–į –§–ĺ—Ä—ā–Ķ –Ī—č–Ľ–ĺ –Ī—č –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ĺ–ĺ –Ņ–ĺ—Ā–ľ–ĺ—ā—Ä–Ķ—ā—Ć, –∑–ī–Ķ—Ā—Ć –Ĺ–į —Ą–ĺ—Ä—É–ľ–Ķ –≤—Ä–ĺ–ī–Ķ –Ī—č–Ľ–į —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–į—Ź —ā–Ķ–ľ–į, –Ĺ–ĺ —Ā—Ā—č–Ľ–ļ–ł —ā–į–ľ –ī–į–≤–Ĺ–ĺ –Ņ—Ä–ĺ—ā—É—Ö–Ľ–ł.

–ü—Ä–ĺ —Ā2forth –ĺ—ā mpe —Ź –≤—Ä–ĺ–ī–Ķ —á–ł—ā–į–Ľ –ļ–ĺ–≥–ī–į-—ā–ĺ –ī–į–≤–Ĺ–ĺ, —á—ā–ĺ-—ā–ĺ —ā–į–ļ–ĺ–Ķ –Ņ—Ä–ł–Ņ–ĺ–ľ–ł–Ĺ–į—é —Ā–ľ—É—ā–Ĺ–ĺ, —ā–į–ľ —É –Ĺ–ł—Ö –ļ–į–∂–ł—Ā—Ć –ī–į–∂–Ķ float –Ĺ–Ķ –∑–į–≤–Ķ–∑–Ľ–ł, –Ĺ–ĺ –ľ–ĺ–≥—É –ĺ—ą–ł–Ī–į—ā—Ć—Ā—Ź. –ė –ĺ—Ä–ł–≥–ł–Ĺ–į–Ľ—Ć–Ĺ—č–Ļ LCC –≤—Ä–ĺ–ī–Ķ —Ā–ľ–ĺ—ā—Ä–Ķ–Ľ, –ľ–Ĺ–Ķ –ĺ–Ĺ –Ņ–ĺ–ļ–į–∑–į–Ľ—Ā—Ź –ļ–į–ļ–ł–ľ-—ā–ĺ –≥—Ä–ĺ–ľ–ĺ–∑–ī–ļ–ł–ľ. :)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°–Ī —Ā–Ķ–Ĺ 30, 2023 19:50 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

Total Vacuum –Ņ–ł—Ā–į–Ľ(–į): –°–ĺ–Ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, –Ĺ–Ķ–Ī–ĺ–Ľ—Ć—ą–į—Ź –Ņ—Ä–ĺ–Ī–į –Ņ–Ķ—Ä–į —Ā —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–Ķ–Ļ —Ā–ł-–≤-—Ą–ĺ—Ä—ā.. –ź, —á–Ķ–ľ "–Ņ–Ľ–ĺ—Ö" –≤–į—Ä–ł–į–Ĺ—ā –ł—Ā–Ņ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź –§–ĺ—Ä—ā –ī–Ľ—Ź –ī–Ľ—Ź —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–ł –°–ł? –ú–ĺ–≥—É —Ā–ļ–ł–Ĺ—É—ā—Ć —Ā–≤–ĺ–Ļ –≤–į—Ä–ł–į–Ĺ—ā –Ņ—Ä–ĺ—ā–ĺ—ā–ł–Ņ–į LCC -> SPf4 (–ī–Ķ–Ľ–į–Ľ—Ā—Ź –Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ C2Forth on Mpe Ltd —Ā –ł—Ö —Ā–į–Ļ—ā–į) –ł –≤–į—Ä–ł–į–Ĺ—ā –ĺ—ā –ú–ł—Ö–į–ł–Ľ–į. (–ĺ–Ĺ –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑–ĺ–≤—č–≤–į–Ľ LCC —Ą—Ä–ĺ–Ĺ—ā-end –≤ –ļ–ĺ–ī SPF4), —É –ľ–Ķ–Ĺ—Ź LCC –ĺ—ā –°–ł (—Ā–Ī–ĺ—Ä–ļ–į –Ĺ–į PellesC), –į –Ī–ł–Ī–Ľ–ł–ĺ—ā–Ķ–ļ–ł (stdlib, stdio ...) —É–∂–Ķ –Ĺ–į SPF4 (—ā–ĺ–Ņ–ł–ļ –Ķ—Ā—ā—Ć –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ) Total Vacuum –Ņ–ł—Ā–į–Ľ(–į): –ü–ĺ–Ľ–Ķ–∑–Ĺ—č–Ļ –ł–Ĺ—Ā—ā—Ä—É–ľ–Ķ–Ĺ—ā –≤—č—Ä–ł—Ā–ĺ–≤—č–≤–į–Ķ—ā—Ā—Ź. –Ē–į–∂–Ķ –Ĺ–Ķ—Ā–ľ–ĺ—ā—Ä—Ź –Ĺ–į –Ķ–≥–ĺ –ĺ—ā–Ĺ–ĺ—Ā–ł—ā–Ķ–Ľ—Ć–Ĺ—É—é –Ņ—Ä–ł–ľ–ł—ā–ł–≤–Ĺ–ĺ—Ā—ā—Ć –ł —Ā–Ľ–į–Ī–ĺ–Ķ –ļ–į—á–Ķ—Ā—ā–≤–ĺ –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ–ĺ–≥–ĺ –ļ–ĺ–ī–į.  –Ę–į–ļ —á—ā–ĺ –Ī—É–ī–Ķ—ā –ł –Ņ–ĺ–ī –ľ–ĺ–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ņ—Ä–ĺ—Ā—ā–Ķ–Ĺ—Ć–ļ–ł–Ļ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–ł. –Ē–į, —ā–ĺ–∂–Ķ —Ā—ā–ĺ–Ľ–ļ–Ĺ—É–Ľ—Ā—Ź, —á—ā–ĺ –ł –ú–į–ļ—Ä–ĺ-–ĺ–Ņ—ā–ł–ľ–ł–∑–į—ā–ĺ—Ä –≤ SPF4 —É–∂–Ķ –Ĺ–Ķ —Ā–Ņ—Ä–į–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ā –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–Ķ–Ļ –Ņ–ĺ–Ľ—É—á–Ķ–Ĺ–Ĺ–ĺ–≥–ĺ –ļ–ĺ–ī–į SPF4. –Ě–į VFX Forth –Ĺ–Ķ –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź–Ľ - –ľ–ĺ–∂–Ķ—ā —ā–į–ľ –Ľ—É—á—ą–Ķ —ć—ā–ĺ –Ņ–ĺ–Ľ—É—á–į–Ķ—ā—Ā—Ź. –ź, —Ä–į–Ī–ĺ—ā—É –ľ–į–ļ—Ä–ĺ-–ĺ–Ņ—ā–ł–ľ–ł–∑–į—ā–ĺ—Ä–į –≤ SPF4, –≤–Ķ—Ä–ĺ—Ź—ā–Ĺ–ĺ, –ľ–ĺ–∂–Ķ—ā –ĺ–Ī—ä—Ź—Ā–Ĺ–ł—ā—Ć —ā–ĺ–Ľ—Ć–ļ–ĺ –ú–ł—Ö–į–ł–Ľ.  –Ď—č–Ľ –Ķ—Č—Ď –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ĺ—č–Ļ –Ņ—Ä–ĺ–Ķ–ļ—ā F-- –ī–Ľ—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź –§–ĺ—Ä—ā –ł –°–ł —Ā–ĺ–≤–ľ–Ķ—Ā—ā–Ĺ–ĺ. P.S. –ź, –≤–ĺ–ĺ–Ī—Č–Ķ, –Ī–ĺ–Ľ–Ķ–Ķ –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ķ–Ĺ –≤–į—Ä–ł–į–Ĺ—ā —ā—Ä–į–Ĺ—Ā–Ņ–ł–Ľ—Ź—Ü–ł–ł –§–ĺ—Ä—ā –≤ –°–ł. –í —ć—ā–ĺ–ľ –Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–ł —ā–ĺ–∂–Ķ —Ā—É—Č–Ķ—Ā—ā–≤—É—é—ā –Ĺ–Ķ–ļ–ĺ—ā–ĺ—Ä—č–Ķ —Ä–į–∑—Ä–į–Ī–ĺ—ā–ļ–ł, –Ĺ–į—á–ł–Ĺ–į—Ź –ĺ—ā Timbre –≥–ī–Ķ –§–ĺ—Ä—ā –ļ–ĺ–ī –Ņ–ĺ –Ņ—Ä–į–≤–ł–Ľ–į–ľ –Ĺ–į –§–ĺ—Ä—ā –Ņ–ĺ–ī–ĺ–Ī–Ĺ–ĺ–ľ —Ź–∑—č–ļ–Ķ –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑—É–Ķ—ā—Ā—Ź –≤ –°–ł. –Į —ā—É—ā –Ĺ–Ķ–ľ–Ĺ–ĺ–≥–ĺ "—É–≤–Ľ—Ď–ļ—Ā—Ź" —Ā–Ī–ĺ—Ä–ļ–ĺ–Ļ Linux Puppy (Xenial) —Ā –≤–į—Ä–ł–į–Ĺ—ā–į –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź —Ā–ĺ–Ī–ł—Ä–į–Ĺ–ł—Ź GLibc-2.33 –ł–∑ –ł—Ā—Ö–ĺ–ī–Ĺ–ł–ļ–ĺ–≤ –ī–Ľ—Ź –∑–į–Ņ—É—Ā–ļ–į, –í —ć—ā–ĺ–ľ —ā–ĺ–Ņ–ł–ļ–Ķ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź, –Ĺ–ĺ –Ņ–ĺ—Ö–ĺ–∂–Ķ –Ī–Ķ–∑ —Ā–Ī–ĺ—Ä–ļ–ł Xorg (–ł –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ –Ķ—Č—Ď —á–Ķ–≥–ĺ –Ľ–ł–Ī–ĺ) —ć—ā–ĺ—ā –≤–į—Ä–ł–į–Ĺ—ā –Ĺ–Ķ –∑–į–Ņ—É—Ā—ā–ł—ā—Ć. –°–Ķ–Ļ—á–į—Ā –ī—É–ľ–į—é –ļ–į–ļ –∑–į–Ņ—É—Ā—ā–ł—ā—Ć –≤–Ķ–Ĺ—ā–ł–Ľ—Ź—ā–ĺ—Ä –≤ –Ī—É–ļ–Ķ, —á—ā–ĺ–Ī—č –Ņ—Ä–ł –Ĺ–į–≥—Ä—É–∑–ļ–Ķ –Ī—É–ļ –ľ–ĺ–∂–Ĺ–ĺ –Ī—č–Ľ–ĺ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć. [quote="Total Vacuum"]–°–ĺ–Ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, –Ĺ–Ķ–Ī–ĺ–Ľ—Ć—ą–į—Ź –Ņ—Ä–ĺ–Ī–į –Ņ–Ķ—Ä–į —Ā —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–Ķ–Ļ —Ā–ł-–≤-—Ą–ĺ—Ä—ā..[/quote]

–ź, —á–Ķ–ľ "–Ņ–Ľ–ĺ—Ö" –≤–į—Ä–ł–į–Ĺ—ā –ł—Ā–Ņ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź –§–ĺ—Ä—ā –ī–Ľ—Ź –ī–Ľ—Ź —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–ł –°–ł?

–ú–ĺ–≥—É —Ā–ļ–ł–Ĺ—É—ā—Ć —Ā–≤–ĺ–Ļ –≤–į—Ä–ł–į–Ĺ—ā –Ņ—Ä–ĺ—ā–ĺ—ā–ł–Ņ–į LCC -> SPf4 (–ī–Ķ–Ľ–į–Ľ—Ā—Ź –Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ C2Forth on Mpe Ltd —Ā –ł—Ö —Ā–į–Ļ—ā–į)

–ł –≤–į—Ä–ł–į–Ĺ—ā –ĺ—ā –ú–ł—Ö–į–ł–Ľ–į. (–ĺ–Ĺ –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑–ĺ–≤—č–≤–į–Ľ LCC —Ą—Ä–ĺ–Ĺ—ā-end –≤ –ļ–ĺ–ī SPF4), —É –ľ–Ķ–Ĺ—Ź LCC –ĺ—ā –°–ł (—Ā–Ī–ĺ—Ä–ļ–į –Ĺ–į PellesC),

–į –Ī–ł–Ī–Ľ–ł–ĺ—ā–Ķ–ļ–ł (stdlib, stdio ...) —É–∂–Ķ –Ĺ–į SPF4 (—ā–ĺ–Ņ–ł–ļ –Ķ—Ā—ā—Ć –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ)

[quote="Total Vacuum"]–ü–ĺ–Ľ–Ķ–∑–Ĺ—č–Ļ –ł–Ĺ—Ā—ā—Ä—É–ľ–Ķ–Ĺ—ā –≤—č—Ä–ł—Ā–ĺ–≤—č–≤–į–Ķ—ā—Ā—Ź. –Ē–į–∂–Ķ –Ĺ–Ķ—Ā–ľ–ĺ—ā—Ä—Ź –Ĺ–į –Ķ–≥–ĺ –ĺ—ā–Ĺ–ĺ—Ā–ł—ā–Ķ–Ľ—Ć–Ĺ—É—é –Ņ—Ä–ł–ľ–ł—ā–ł–≤–Ĺ–ĺ—Ā—ā—Ć –ł —Ā–Ľ–į–Ī–ĺ–Ķ –ļ–į—á–Ķ—Ā—ā–≤–ĺ –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ–ĺ–≥–ĺ –ļ–ĺ–ī–į. :) –Ę–į–ļ —á—ā–ĺ –Ī—É–ī–Ķ—ā –ł –Ņ–ĺ–ī –ľ–ĺ–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ņ—Ä–ĺ—Ā—ā–Ķ–Ĺ—Ć–ļ–ł–Ļ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–ł.[/quote]

–Ē–į, —ā–ĺ–∂–Ķ —Ā—ā–ĺ–Ľ–ļ–Ĺ—É–Ľ—Ā—Ź, —á—ā–ĺ –ł –ú–į–ļ—Ä–ĺ-–ĺ–Ņ—ā–ł–ľ–ł–∑–į—ā–ĺ—Ä –≤ SPF4 —É–∂–Ķ –Ĺ–Ķ —Ā–Ņ—Ä–į–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ā –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–Ķ–Ļ –Ņ–ĺ–Ľ—É—á–Ķ–Ĺ–Ĺ–ĺ–≥–ĺ –ļ–ĺ–ī–į SPF4.

–Ě–į VFX Forth –Ĺ–Ķ –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź–Ľ - –ľ–ĺ–∂–Ķ—ā —ā–į–ľ –Ľ—É—á—ą–Ķ —ć—ā–ĺ –Ņ–ĺ–Ľ—É—á–į–Ķ—ā—Ā—Ź.

–ź, —Ä–į–Ī–ĺ—ā—É –ľ–į–ļ—Ä–ĺ-–ĺ–Ņ—ā–ł–ľ–ł–∑–į—ā–ĺ—Ä–į –≤ SPF4, –≤–Ķ—Ä–ĺ—Ź—ā–Ĺ–ĺ, –ľ–ĺ–∂–Ķ—ā –ĺ–Ī—ä—Ź—Ā–Ĺ–ł—ā—Ć —ā–ĺ–Ľ—Ć–ļ–ĺ –ú–ł—Ö–į–ł–Ľ. :)

–Ď—č–Ľ –Ķ—Č—Ď –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ĺ—č–Ļ –Ņ—Ä–ĺ–Ķ–ļ—ā [url=https://fminus.sourceforge.net/]F--[/url] –ī–Ľ—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź –§–ĺ—Ä—ā –ł –°–ł —Ā–ĺ–≤–ľ–Ķ—Ā—ā–Ĺ–ĺ.

P.S. –ź, –≤–ĺ–ĺ–Ī—Č–Ķ, –Ī–ĺ–Ľ–Ķ–Ķ –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ķ–Ĺ –≤–į—Ä–ł–į–Ĺ—ā —ā—Ä–į–Ĺ—Ā–Ņ–ł–Ľ—Ź—Ü–ł–ł –§–ĺ—Ä—ā –≤ –°–ł.

–í —ć—ā–ĺ–ľ –Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–ł —ā–ĺ–∂–Ķ —Ā—É—Č–Ķ—Ā—ā–≤—É—é—ā –Ĺ–Ķ–ļ–ĺ—ā–ĺ—Ä—č–Ķ —Ä–į–∑—Ä–į–Ī–ĺ—ā–ļ–ł, –Ĺ–į—á–ł–Ĺ–į—Ź –ĺ—ā Timbre –≥–ī–Ķ –§–ĺ—Ä—ā –ļ–ĺ–ī –Ņ–ĺ –Ņ—Ä–į–≤–ł–Ľ–į–ľ –Ĺ–į

–§–ĺ—Ä—ā –Ņ–ĺ–ī–ĺ–Ī–Ĺ–ĺ–ľ —Ź–∑—č–ļ–Ķ –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑—É–Ķ—ā—Ā—Ź –≤ –°–ł.

–Į —ā—É—ā –Ĺ–Ķ–ľ–Ĺ–ĺ–≥–ĺ "—É–≤–Ľ—Ď–ļ—Ā—Ź" —Ā–Ī–ĺ—Ä–ļ–ĺ–Ļ Linux Puppy (Xenial) —Ā –≤–į—Ä–ł–į–Ĺ—ā–į –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—Ź —Ā–ĺ–Ī–ł—Ä–į–Ĺ–ł—Ź GLibc-2.33 –ł–∑ –ł—Ā—Ö–ĺ–ī–Ĺ–ł–ļ–ĺ–≤ –ī–Ľ—Ź –∑–į–Ņ—É—Ā–ļ–į,

[url=https://forum.puppyrus.org/index.php?topic=24137.msg187077#msg187077]–í —ć—ā–ĺ–ľ —ā–ĺ–Ņ–ł–ļ–Ķ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź[/url],

–Ĺ–ĺ –Ņ–ĺ—Ö–ĺ–∂–Ķ –Ī–Ķ–∑ —Ā–Ī–ĺ—Ä–ļ–ł Xorg (–ł –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ –Ķ—Č—Ď —á–Ķ–≥–ĺ –Ľ–ł–Ī–ĺ) —ć—ā–ĺ—ā –≤–į—Ä–ł–į–Ĺ—ā –Ĺ–Ķ –∑–į–Ņ—É—Ā—ā–ł—ā—Ć.

–°–Ķ–Ļ—á–į—Ā –ī—É–ľ–į—é –ļ–į–ļ –∑–į–Ņ—É—Ā—ā–ł—ā—Ć –≤–Ķ–Ĺ—ā–ł–Ľ—Ź—ā–ĺ—Ä –≤ –Ī—É–ļ–Ķ, —á—ā–ĺ–Ī—č –Ņ—Ä–ł –Ĺ–į–≥—Ä—É–∑–ļ–Ķ –Ī—É–ļ –ľ–ĺ–∂–Ĺ–ĺ –Ī—č–Ľ–ĺ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć.

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –ü—ā —Ā–Ķ–Ĺ 29, 2023 12:31 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

–Ě—É —ā–į–ļ –ł —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤ –ł–ī–Ķ–į–Ľ–Ķ –≤—Ä–ĺ–ī–Ķ –ļ–į–ļ –Ĺ–Ķ –≥–ł–≥–į–Ĺ—ā—Ā–ļ–ł–Ļ... –°–ĺ–Ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, –Ĺ–Ķ–Ī–ĺ–Ľ—Ć—ą–į—Ź –Ņ—Ä–ĺ–Ī–į –Ņ–Ķ—Ä–į —Ā —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–Ķ–Ļ —Ā–ł-–≤-—Ą–ĺ—Ä—ā. –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, —ā–į–ļ–ĺ–Ļ –ļ–ĺ–ī –ö–ĺ–ī: void emit ( char c ) ;

void type ( char * s ) ;

int i ;

struct node {

char n ;

struct node * next ;

} * list , nodes [ 256 ] ;

void main ( ) {

for ( i = 0 ; i < 256 ; i = i + 1 ) nodes [ i ] . n = i ;

nodes [ 'l' ] . next = & nodes [ 'i' ] ;

nodes [ 'i' ] . next = & nodes [ 's' ] ;

nodes [ 's' ] . next = & nodes [ 't' ] ;

nodes [ 't' ] . next = 0 ;

list = & nodes [ 'l' ] ;

while ( list ) {

emit ( list -> n ) ;

type ( "->" ) ;

list = list -> next ;

}

type ( "NULL" ) ;

} –Ņ—Ä–Ķ–≤—Ä–į—Č–į–Ķ—ā—Ā—Ź –≤ —ā–į–ļ–ĺ–Ķ (—Ą–ĺ—Ä–ľ–į—ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ —Ā–ī–Ķ–Ľ–į–Ĺ–ĺ –≤—Ä—É—á–Ĺ—É—é): –ö–ĺ–ī: create i 1 cells allot

create list 1 cells allot

create nodes 512 cells allot

: main

i 0 over ! @ drop begin i @ 256 < while

nodes i @ 16 * + 0 + i @ over c! c@ drop

i i @ 1 + over ! @ drop repeat

nodes 'l' 16 * + 8 + nodes 'i' 16 * + over ! @ drop

nodes 'i' 16 * + 8 + nodes 's' 16 * + over ! @ drop

nodes 's' 16 * + 8 + nodes 't' 16 * + over ! @ drop

nodes 't' 16 * + 8 + 0 over ! @ drop

list nodes 'l' 16 * + over ! @ drop

begin list @ while

list @ 0 + c@ emit

s" ->" type

list list @ 8 + @ over ! @ drop

repeat

s" NULL" type

;

main –≤—č–≤–ĺ–ī–ł—ā: –ö–ĺ–ī: l->i->s->t->NULL –Ď–Ķ–∑—É—Ā–Ľ–ĺ–≤–Ĺ–ĺ, –≤—č—Ö–Ľ–ĺ–Ņ –Ī–Ķ–∑ –ļ–į–ļ–ł—Ö-–Ľ–ł–Ī–ĺ –Ĺ–į–ľ–Ķ–ļ–ĺ–≤ –Ĺ–į –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–ł, –Ĺ–ĺ —Ā–į–ľ–ĺ–Ķ –≥–Ľ–į–≤–Ĺ–ĺ–Ķ, —á—ā–ĺ —É–∂–Ķ —Ä–į–Ī–ĺ—ā–į–Ķ—ā (–Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –ľ–ĺ–∂–Ĺ–ĺ –∑–ī–Ķ—Ā—Ć –Ņ—Ä–ĺ—ā–Ķ—Ā—ā–ł—Ä–ĺ–≤–į—ā—Ć). –Ě–Ķ–≤–ĺ–ĺ—Ä—É–∂–Ķ–Ĺ–Ĺ—č–ľ –≤–∑–≥–Ľ—Ź–ī–ĺ–ľ –≤–ł–ī–Ĺ–į –ľ–į—Ā—Ā–į –Ľ–ł—ą–Ĺ–Ķ–≥–ĺ –ļ–ĺ–ī–į. –Ē–į–Ľ—Ć—ą–Ķ –ľ–ĺ–≥—É—ā –Ī—č—ā—Ć —Ä–į–∑–Ĺ—č–Ķ –≤–į—Ä–ł–į–Ĺ—ā—č: - –ĺ—Ā—ā–į–≤–ł—ā—Ć –≤ —ā–į–ļ–ĺ–ľ –≤–ł–ī–Ķ, –Ķ—Ā–Ľ–ł —Ā–ļ–ĺ—Ä–ĺ—Ā—ā—Ć –ł —Ä–į–∑–ľ–Ķ—Ä –ļ–ĺ–ī–į –Ĺ–Ķ –ļ—Ä–ł—ā–ł—á–Ĺ—č; - –ī–ĺ–Ī–į–≤–ł—ā—Ć –Ĺ—É–∂–Ĺ—č–Ķ –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–ł –≤ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä - –Ĺ–Ķ —Ä–į–Ĺ–Ķ–Ķ, —á–Ķ–ľ –∑–į—Ä–į–Ī–ĺ—ā–į–Ķ—ā –≤–Ķ—Ā—Ć –∑–į–Ņ–Ľ–į–Ĺ–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ; - –Ĺ–į–Ī—Ä–ĺ—Ā–į—ā—Ć –ĺ—ā–ī–Ķ–Ľ—Ć–Ĺ—É—é —É—ā–ł–Ľ–ł—ā—É, –ļ–ĺ—ā–ĺ—Ä–į—Ź –Ņ–ĺ–ī—á–ł—Č–į–Ķ—ā –Ľ–ł—ą–Ĺ–ł–Ļ –ļ–ĺ–ī; - –≤—Ä—É—á–Ĺ—É—é –ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į—ā—Ć —É–∑–ļ–ł–Ķ –ľ–Ķ—Ā—ā–į –≤—č—Ö–Ľ–ĺ–Ņ–į. –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, –ľ–ĺ–∂–Ķ—ā –Ņ–ĺ–Ľ—É—á–ł—ā—Ć—Ā—Ź —á—ā–ĺ-—ā–ĺ –≤—Ä–ĺ–ī–Ķ —ā–į–ļ–ĺ–≥–ĺ: –ö–ĺ–ī: create i 1 cells allot

create list 1 cells allot

create nodes 512 cells allot

: main

0 i ! begin i @ 256 < while

i @ nodes i @ 16 * + c!

i @ 1 + i ! repeat

nodes 'i' 16 * + nodes 'l' 16 * + 8 + !

nodes 's' 16 * + nodes 'i' 16 * + 8 + !

nodes 't' 16 * + nodes 's' 16 * + 8 + !

0 nodes 't' 16 * + 8 + !

nodes 'l' 16 * + list !

begin list @ while

list @ c@ emit

s" ->" type

list @ 8 + @ list !

repeat

s" NULL" type

;

main –Ē–į–Ľ–Ķ–Ķ, –Ķ—Ā–Ľ–ł –Ĺ–į–ī–ĺ —É–ľ–Ķ–Ĺ—Ć—ą–ł—ā—Ć —Ä–į–∑–ľ–Ķ—Ä –ł–Ľ–ł –Ņ–ĺ–≤—č—Ā–ł—ā—Ć —á–ł—ā–į–Ķ–ľ–ĺ—Ā—ā—Ć –ļ–ĺ–ī–į, –ľ–ĺ–∂–Ĺ–ĺ –ĺ–Ī—č–≥—Ä–į—ā—Ć: –ö–ĺ–ī: : nodes[i] 16 * nodes + ;

: .n ;

: .next 8 + ;

: ->n @ .n ;

: ->next @ .next ; –ł —ā.–ī. –ł —ā.–Ņ. –Ě—É –ł–Ľ–ł, –ī–ĺ–Ņ—É—Ā—ā–ł–ľ, –ī–Ľ—Ź —Ą–į–ļ—ā–ĺ—Ä–ł–į–Ľ–į –ö–ĺ–ī: void recurse ( ) ;

void cr ( ) ;

void emit ( char c ) ;

int fac ( char n ) {

if ( n ) return n * recurse ( n - 1 ) ; else return 1 ;

}

int n , r ;

void main ( ) {

n = 6 ; while ( n ) {

n = n - 1 ;

r = fac ( n ) ;

while ( r ) { emit ( '.' ) ; r = r - 1 ; }

cr ( ) ;

}

} –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ –ö–ĺ–ī: : fac 0 pick if 0 pick 1 pick 1 - recurse * nip exit else 1 nip exit then ;

create n 1 cells allot

create r 1 cells allot

: main

n 6 over ! @ drop begin n @ while

n n @ 1 - over ! @ drop

r n @ fac over ! @ drop

begin r @ while '.' emit r r @ 1 - over ! @ drop repeat

cr

repeat

;

main , –ļ–ĺ—ā–ĺ—Ä–ĺ–Ķ –Ņ–ĺ—Ā–Ľ–Ķ –Ņ–į—Ä—č —Ä—É—á–Ĺ—č—Ö –Ņ—Ä–į–≤–ĺ–ļ –Ņ—Ä–Ķ–≤—Ä–į—Č–į–Ķ—ā—Ā—Ź –≤ –ö–ĺ–ī: : fac dup if dup dup 1 - recurse * else 1 then nip ;

create n 1 cells allot

create r 1 cells allot

: main

6 n ! begin n @ while

n @ 1 - n !

n @ fac r !

begin r @ while '.' emit r @ 1 - r ! repeat

cr

repeat

;

main –ü–ĺ–Ľ–Ķ–∑–Ĺ—č–Ļ –ł–Ĺ—Ā—ā—Ä—É–ľ–Ķ–Ĺ—ā –≤—č—Ä–ł—Ā–ĺ–≤—č–≤–į–Ķ—ā—Ā—Ź. –Ē–į–∂–Ķ –Ĺ–Ķ—Ā–ľ–ĺ—ā—Ä—Ź –Ĺ–į –Ķ–≥–ĺ –ĺ—ā–Ĺ–ĺ—Ā–ł—ā–Ķ–Ľ—Ć–Ĺ—É—é –Ņ—Ä–ł–ľ–ł—ā–ł–≤–Ĺ–ĺ—Ā—ā—Ć –ł —Ā–Ľ–į–Ī–ĺ–Ķ –ļ–į—á–Ķ—Ā—ā–≤–ĺ –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ–ĺ–≥–ĺ –ļ–ĺ–ī–į.  –Ę–į–ļ —á—ā–ĺ –Ī—É–ī–Ķ—ā –ł –Ņ–ĺ–ī –ľ–ĺ–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ņ—Ä–ĺ—Ā—ā–Ķ–Ĺ—Ć–ļ–ł–Ļ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–ł. :D –Ě—É —ā–į–ļ –ł —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤ –ł–ī–Ķ–į–Ľ–Ķ –≤—Ä–ĺ–ī–Ķ –ļ–į–ļ –Ĺ–Ķ –≥–ł–≥–į–Ĺ—ā—Ā–ļ–ł–Ļ...

–°–ĺ–Ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, –Ĺ–Ķ–Ī–ĺ–Ľ—Ć—ą–į—Ź –Ņ—Ä–ĺ–Ī–į –Ņ–Ķ—Ä–į —Ā —ā—Ä–į–Ĺ—Ā–Ľ—Ź—Ü–ł–Ķ–Ļ —Ā–ł-–≤-—Ą–ĺ—Ä—ā.

–Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, —ā–į–ļ–ĺ–Ļ –ļ–ĺ–ī[code]void emit ( char c ) ;

void type ( char * s ) ;

int i ;

struct node {

char n ;

struct node * next ;

} * list , nodes [ 256 ] ;

void main ( ) {

for ( i = 0 ; i < 256 ; i = i + 1 ) nodes [ i ] . n = i ;

nodes [ 'l' ] . next = & nodes [ 'i' ] ;

nodes [ 'i' ] . next = & nodes [ 's' ] ;

nodes [ 's' ] . next = & nodes [ 't' ] ;

nodes [ 't' ] . next = 0 ;

list = & nodes [ 'l' ] ;

while ( list ) {

emit ( list -> n ) ;

type ( "->" ) ;

list = list -> next ;

}

type ( "NULL" ) ;

}[/code]–Ņ—Ä–Ķ–≤—Ä–į—Č–į–Ķ—ā—Ā—Ź –≤ —ā–į–ļ–ĺ–Ķ (—Ą–ĺ—Ä–ľ–į—ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ —Ā–ī–Ķ–Ľ–į–Ĺ–ĺ –≤—Ä—É—á–Ĺ—É—é):[code]create i 1 cells allot

create list 1 cells allot

create nodes 512 cells allot

: main

i 0 over ! @ drop begin i @ 256 < while

nodes i @ 16 * + 0 + i @ over c! c@ drop

i i @ 1 + over ! @ drop repeat

nodes 'l' 16 * + 8 + nodes 'i' 16 * + over ! @ drop

nodes 'i' 16 * + 8 + nodes 's' 16 * + over ! @ drop

nodes 's' 16 * + 8 + nodes 't' 16 * + over ! @ drop

nodes 't' 16 * + 8 + 0 over ! @ drop

list nodes 'l' 16 * + over ! @ drop

begin list @ while

list @ 0 + c@ emit

s" ->" type

list list @ 8 + @ over ! @ drop

repeat

s" NULL" type

;

main[/code]–≤—č–≤–ĺ–ī–ł—ā:[code]l->i->s->t->NULL[/code]–Ď–Ķ–∑—É—Ā–Ľ–ĺ–≤–Ĺ–ĺ, –≤—č—Ö–Ľ–ĺ–Ņ –Ī–Ķ–∑ –ļ–į–ļ–ł—Ö-–Ľ–ł–Ī–ĺ –Ĺ–į–ľ–Ķ–ļ–ĺ–≤ –Ĺ–į –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–ł, –Ĺ–ĺ —Ā–į–ľ–ĺ–Ķ –≥–Ľ–į–≤–Ĺ–ĺ–Ķ, —á—ā–ĺ —É–∂–Ķ —Ä–į–Ī–ĺ—ā–į–Ķ—ā (–Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –ľ–ĺ–∂–Ĺ–ĺ [url=https://www.jdoodle.com/execute-forth-online/]–∑–ī–Ķ—Ā—Ć[/url] –Ņ—Ä–ĺ—ā–Ķ—Ā—ā–ł—Ä–ĺ–≤–į—ā—Ć). –Ě–Ķ–≤–ĺ–ĺ—Ä—É–∂–Ķ–Ĺ–Ĺ—č–ľ –≤–∑–≥–Ľ—Ź–ī–ĺ–ľ –≤–ł–ī–Ĺ–į –ľ–į—Ā—Ā–į –Ľ–ł—ą–Ĺ–Ķ–≥–ĺ –ļ–ĺ–ī–į. –Ē–į–Ľ—Ć—ą–Ķ –ľ–ĺ–≥—É—ā –Ī—č—ā—Ć —Ä–į–∑–Ĺ—č–Ķ –≤–į—Ä–ł–į–Ĺ—ā—č:

- –ĺ—Ā—ā–į–≤–ł—ā—Ć –≤ —ā–į–ļ–ĺ–ľ –≤–ł–ī–Ķ, –Ķ—Ā–Ľ–ł —Ā–ļ–ĺ—Ä–ĺ—Ā—ā—Ć –ł —Ä–į–∑–ľ–Ķ—Ä –ļ–ĺ–ī–į –Ĺ–Ķ –ļ—Ä–ł—ā–ł—á–Ĺ—č;

- –ī–ĺ–Ī–į–≤–ł—ā—Ć –Ĺ—É–∂–Ĺ—č–Ķ –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–ł –≤ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä - –Ĺ–Ķ —Ä–į–Ĺ–Ķ–Ķ, —á–Ķ–ľ –∑–į—Ä–į–Ī–ĺ—ā–į–Ķ—ā –≤–Ķ—Ā—Ć –∑–į–Ņ–Ľ–į–Ĺ–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–Ļ —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ;

- –Ĺ–į–Ī—Ä–ĺ—Ā–į—ā—Ć –ĺ—ā–ī–Ķ–Ľ—Ć–Ĺ—É—é —É—ā–ł–Ľ–ł—ā—É, –ļ–ĺ—ā–ĺ—Ä–į—Ź –Ņ–ĺ–ī—á–ł—Č–į–Ķ—ā –Ľ–ł—ą–Ĺ–ł–Ļ –ļ–ĺ–ī;

- –≤—Ä—É—á–Ĺ—É—é –ĺ–Ņ—ā–ł–ľ–ł–∑–ł—Ä–ĺ–≤–į—ā—Ć —É–∑–ļ–ł–Ķ –ľ–Ķ—Ā—ā–į –≤—č—Ö–Ľ–ĺ–Ņ–į.

–Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, –ľ–ĺ–∂–Ķ—ā –Ņ–ĺ–Ľ—É—á–ł—ā—Ć—Ā—Ź —á—ā–ĺ-—ā–ĺ –≤—Ä–ĺ–ī–Ķ —ā–į–ļ–ĺ–≥–ĺ:[code]create i 1 cells allot

create list 1 cells allot

create nodes 512 cells allot

: main

0 i ! begin i @ 256 < while

i @ nodes i @ 16 * + c!

i @ 1 + i ! repeat

nodes 'i' 16 * + nodes 'l' 16 * + 8 + !

nodes 's' 16 * + nodes 'i' 16 * + 8 + !

nodes 't' 16 * + nodes 's' 16 * + 8 + !

0 nodes 't' 16 * + 8 + !

nodes 'l' 16 * + list !

begin list @ while

list @ c@ emit

s" ->" type

list @ 8 + @ list !

repeat

s" NULL" type

;

main[/code]–Ē–į–Ľ–Ķ–Ķ, –Ķ—Ā–Ľ–ł –Ĺ–į–ī–ĺ —É–ľ–Ķ–Ĺ—Ć—ą–ł—ā—Ć —Ä–į–∑–ľ–Ķ—Ä –ł–Ľ–ł –Ņ–ĺ–≤—č—Ā–ł—ā—Ć —á–ł—ā–į–Ķ–ľ–ĺ—Ā—ā—Ć –ļ–ĺ–ī–į, –ľ–ĺ–∂–Ĺ–ĺ –ĺ–Ī—č–≥—Ä–į—ā—Ć:[code]: nodes[i] 16 * nodes + ;

: .n ;

: .next 8 + ;

: ->n @ .n ;

: ->next @ .next ;[/code]–ł —ā.–ī. –ł —ā.–Ņ.

–Ě—É –ł–Ľ–ł, –ī–ĺ–Ņ—É—Ā—ā–ł–ľ, –ī–Ľ—Ź —Ą–į–ļ—ā–ĺ—Ä–ł–į–Ľ–į[code]void recurse ( ) ;

void cr ( ) ;

void emit ( char c ) ;

int fac ( char n ) {

if ( n ) return n * recurse ( n - 1 ) ; else return 1 ;

}

int n , r ;

void main ( ) {

n = 6 ; while ( n ) {

n = n - 1 ;

r = fac ( n ) ;

while ( r ) { emit ( '.' ) ; r = r - 1 ; }

cr ( ) ;

}

}[/code]–Ņ–ĺ–Ľ—É—á–į–Ķ–ľ[code]: fac 0 pick if 0 pick 1 pick 1 - recurse * nip exit else 1 nip exit then ;

create n 1 cells allot

create r 1 cells allot

: main

n 6 over ! @ drop begin n @ while

n n @ 1 - over ! @ drop

r n @ fac over ! @ drop

begin r @ while '.' emit r r @ 1 - over ! @ drop repeat

cr

repeat

;

main[/code], –ļ–ĺ—ā–ĺ—Ä–ĺ–Ķ –Ņ–ĺ—Ā–Ľ–Ķ –Ņ–į—Ä—č —Ä—É—á–Ĺ—č—Ö –Ņ—Ä–į–≤–ĺ–ļ –Ņ—Ä–Ķ–≤—Ä–į—Č–į–Ķ—ā—Ā—Ź –≤[code]: fac dup if dup dup 1 - recurse * else 1 then nip ;

create n 1 cells allot

create r 1 cells allot

: main

6 n ! begin n @ while

n @ 1 - n !

n @ fac r !

begin r @ while '.' emit r @ 1 - r ! repeat

cr

repeat

;

main[/code]

–ü–ĺ–Ľ–Ķ–∑–Ĺ—č–Ļ –ł–Ĺ—Ā—ā—Ä—É–ľ–Ķ–Ĺ—ā –≤—č—Ä–ł—Ā–ĺ–≤—č–≤–į–Ķ—ā—Ā—Ź. –Ē–į–∂–Ķ –Ĺ–Ķ—Ā–ľ–ĺ—ā—Ä—Ź –Ĺ–į –Ķ–≥–ĺ –ĺ—ā–Ĺ–ĺ—Ā–ł—ā–Ķ–Ľ—Ć–Ĺ—É—é –Ņ—Ä–ł–ľ–ł—ā–ł–≤–Ĺ–ĺ—Ā—ā—Ć –ł —Ā–Ľ–į–Ī–ĺ–Ķ –ļ–į—á–Ķ—Ā—ā–≤–ĺ –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ–ĺ–≥–ĺ –ļ–ĺ–ī–į. :) –Ę–į–ļ —á—ā–ĺ –Ī—É–ī–Ķ—ā –ł –Ņ–ĺ–ī –ľ–ĺ–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ņ—Ä–ĺ—Ā—ā–Ķ–Ĺ—Ć–ļ–ł–Ļ –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–ł.

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –ü—ā —Ā–Ķ–Ĺ 29, 2023 00:37 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

Total Vacuum –Ņ–ł—Ā–į–Ľ(–į): tinytapeout - –ļ–Ľ–į—Ā—Ā–Ĺ–į—Ź –∑–į–ī—É–ľ–ļ–į, –Ĺ–ĺ —Ź –ī–ĺ —ā–į–ļ–ĺ–≥–ĺ –Ĺ–Ķ –ī–ĺ—Ä–ĺ—Ā –Ķ—Č–Ķ –ü–õ–ė–° –≤—Ā–Ķ-—ā–į–ļ–ł –Ľ—É—á—ą–Ķ. Tinytapeout —Ā–Ľ–ł—ą–ļ–ĺ–ľ –ľ–į–Ľ–Ķ–Ĺ—Ć–ļ–ł–Ļ, –Ņ—Ä–ĺ—Ā—ā–ĺ —á—Ä–Ķ–∑–ľ–Ķ—Ä–Ĺ–ĺ. –ě–ī–Ĺ–ĺ –Ĺ–į–∑–≤–į–Ĺ–ł–Ķ "–ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–į", –į –Ņ–ĺ —Ā—É—ā–ł —Ā—Ö–Ķ–ľ–į –Ĺ–į –ī–ł—Ā–ļ—Ä–Ķ—ā–Ĺ—č—Ö –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā–į—Ö –Ĺ–Ķ —ā–į–ļ —É–∂ —Ā–ł–Ľ—Ć–Ĺ–ĺ –Ī—É–ī–Ķ—ā –ĺ—ā–Ľ–ł—á–į—ā—Ć—Ā—Ź - —ā–ĺ–∂–Ķ –ļ—Ä–Ķ–ľ–Ĺ–ł–Ļ. [quote="Total Vacuum"]tinytapeout - –ļ–Ľ–į—Ā—Ā–Ĺ–į—Ź –∑–į–ī—É–ľ–ļ–į, –Ĺ–ĺ —Ź –ī–ĺ —ā–į–ļ–ĺ–≥–ĺ –Ĺ–Ķ –ī–ĺ—Ä–ĺ—Ā –Ķ—Č–Ķ [/quote]

–ü–õ–ė–° –≤—Ā–Ķ-—ā–į–ļ–ł –Ľ—É—á—ą–Ķ. Tinytapeout —Ā–Ľ–ł—ą–ļ–ĺ–ľ –ľ–į–Ľ–Ķ–Ĺ—Ć–ļ–ł–Ļ, –Ņ—Ä–ĺ—Ā—ā–ĺ —á—Ä–Ķ–∑–ľ–Ķ—Ä–Ĺ–ĺ. –ě–ī–Ĺ–ĺ –Ĺ–į–∑–≤–į–Ĺ–ł–Ķ "–ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–į", –į –Ņ–ĺ —Ā—É—ā–ł —Ā—Ö–Ķ–ľ–į –Ĺ–į –ī–ł—Ā–ļ—Ä–Ķ—ā–Ĺ—č—Ö –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā–į—Ö –Ĺ–Ķ —ā–į–ļ —É–∂ —Ā–ł–Ľ—Ć–Ĺ–ĺ –Ī—É–ī–Ķ—ā –ĺ—ā–Ľ–ł—á–į—ā—Ć—Ā—Ź - —ā–ĺ–∂–Ķ –ļ—Ä–Ķ–ľ–Ĺ–ł–Ļ.

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –í—Ā —Ā–Ķ–Ĺ 24, 2023 15:03 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

KPG –Ņ–ł—Ā–į–Ľ(–į): –ú–ĺ–∂–Ĺ–ĺ –ĺ—ā—ā–ĺ–Ľ–ļ–Ĺ—É—ā—Ć—Ā—Ź –ĺ—ā —Ä–į–Ĺ–Ķ–Ķ–Ķ —É–∂–Ķ "—Ā–ī–Ķ–Ľ–į–Ĺ–Ĺ—č—Ö" –≤–į—Ä–ł–į–Ĺ—ā–ĺ–≤ (–ł –≤ —Ä–į–ľ–ļ–į—Ö –ĺ–Ī—Ā—É–∂–ī–Ķ–Ĺ–ł—Ź –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ c LCC -> Forth) –ł–Ľ–ł –Ņ–ĺ—Ź–≤–ł—ą–ł—Ö—Ā—Ź –ĺ—Ä–ł–≥–ł–Ĺ–į–Ľ—Ć–Ĺ—č—Ö –ļ–į–ļ –°–°64 –ł/–ł–Ľ–ł –≤—Ä–ĺ–ī–Ķ –≤ DuskOS –ú–Ĺ–Ķ –ļ–į–ļ-—ā–ĺ –Ĺ–Ķ –Ņ–ĺ–Ņ–į–ī–į–Ľ–ł—Ā—Ć —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä—č —Ā–ł-–≤-—Ą–ĺ—Ä—ā. –Ě—É –ł–Ľ–ł –Ņ—Ä–ĺ—Ā—ā–ĺ –Ņ–Ľ–ĺ—Ö–ĺ –ł—Ā–ļ–į–Ľ  –Ē–į –≤ –Ľ—é–Ī–ĺ–ľ —Ā–Ľ—É—á–į–Ķ –Ņ—Ä–ĺ—Č–Ķ —Ā–≤–ĺ–Ļ —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä –Ĺ–į–Ņ–ł—Ā–į—ā—Ć, —á–Ķ–ľ –≤ —á—É–∂–ĺ–ľ —Ä–į–∑–Ī–ł—Ä–į—ā—Ć—Ā—Ź. –£–∂–Ķ —Ā–Ķ–Ļ—á–į—Ā –Ņ—Ä–ĺ—Ā—ā—č–Ķ –Ņ—Ä–ł–ľ–Ķ—Ä—č —ā–ł–Ņ–į —Ą–į–ļ—ā–ĺ—Ä–ł–į–Ľ–į –ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä—É—é—ā—Ā—Ź –≤ uf \ micro forth \ (–Ņ—Ä–ł –∂–Ķ–Ľ–į–Ĺ–ł–ł –ł –≤ –ļ–Ľ–į—Ā—Ā–ł—á–Ķ—Ā–ļ–ł–Ļ —Ą–ĺ—Ä—ā —ā—Ä–ł–≤–ł–į–Ľ—Ć–Ĺ–ĺ –ĺ—ā—ā—Ä–į–Ĺ—Ā–Ľ–ł—Ä—É—é—ā—Ā—Ź) –ł —Ä–į–Ī–ĺ—ā–į—é—ā, –Ĺ—É–∂–Ĺ–ĺ –Ľ–ł—ą—Ć —É—Ā–ł–Ľ–ł–Ķ, —á—ā–ĺ–Ī—č –∑–į—Ā—ā–į–≤–ł—ā—Ć —Ā–Ķ–Ī—Ź –ī–ĺ–≤–Ķ—Ā—ā–ł –ī–ĺ —É–ľ–į. –ź –ļ—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ, –Ľ—é–Ī–ĺ–Ļ —É–≤–į–∂–į—é—Č–ł–Ļ —Ā–Ķ–Ī—Ź –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä –ī–ĺ–Ľ–∂–Ķ–Ĺ —É–ľ–Ķ—ā—Ć –ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä–ĺ–≤–į—ā—Ć —Ā–į–ľ —Ā–Ķ–Ī—Ź, –Ņ–ĺ—ć—ā–ĺ–ľ—É –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–ł –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ī—č—ā—Ć –Ĺ–į–Ņ–ł—Ā–į–Ĺ –Ĺ–į —Ā–ł (—Ź –Ņ–ĺ–ļ–į —Ā–į–ľ —Ā–Ķ–Ī—Ź –Ĺ–Ķ –ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä—É—é, –Ņ–ĺ—ć—ā–ĺ–ľ—É –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ –Ĺ–į tcc –ī–Ķ–Ľ–į—é), –į duskos –ł cc64 –≤—Ä–ĺ–ī–Ķ –Ĺ–į —Ą–ĺ—Ä—ā–Ķ –Ĺ–į–Ņ–ł—Ā–į–Ĺ—č, –Ķ—Ā–Ľ–ł —Ź –Ņ—Ä–į–≤–ł–Ľ—Ć–Ĺ–ĺ –Ņ—É—ā–į—é.  tinytapeout - –ļ–Ľ–į—Ā—Ā–Ĺ–į—Ź –∑–į–ī—É–ľ–ļ–į, –Ĺ–ĺ —Ź –ī–ĺ —ā–į–ļ–ĺ–≥–ĺ –Ĺ–Ķ –ī–ĺ—Ä–ĺ—Ā –Ķ—Č–Ķ  [quote="KPG"]–ú–ĺ–∂–Ĺ–ĺ –ĺ—ā—ā–ĺ–Ľ–ļ–Ĺ—É—ā—Ć—Ā—Ź –ĺ—ā —Ä–į–Ĺ–Ķ–Ķ–Ķ —É–∂–Ķ "—Ā–ī–Ķ–Ľ–į–Ĺ–Ĺ—č—Ö" –≤–į—Ä–ł–į–Ĺ—ā–ĺ–≤ (–ł –≤ —Ä–į–ľ–ļ–į—Ö –ĺ–Ī—Ā—É–∂–ī–Ķ–Ĺ–ł—Ź –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ c LCC -> Forth) –ł–Ľ–ł –Ņ–ĺ—Ź–≤–ł—ą–ł—Ö—Ā—Ź –ĺ—Ä–ł–≥–ł–Ĺ–į–Ľ—Ć–Ĺ—č—Ö –ļ–į–ļ –°–°64 –ł/–ł–Ľ–ł –≤—Ä–ĺ–ī–Ķ –≤ DuskOS[/quote]–ú–Ĺ–Ķ –ļ–į–ļ-—ā–ĺ –Ĺ–Ķ –Ņ–ĺ–Ņ–į–ī–į–Ľ–ł—Ā—Ć —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä—č —Ā–ł-–≤-—Ą–ĺ—Ä—ā. –Ě—É –ł–Ľ–ł –Ņ—Ä–ĺ—Ā—ā–ĺ –Ņ–Ľ–ĺ—Ö–ĺ –ł—Ā–ļ–į–Ľ :) –Ē–į –≤ –Ľ—é–Ī–ĺ–ľ —Ā–Ľ—É—á–į–Ķ –Ņ—Ä–ĺ—Č–Ķ —Ā–≤–ĺ–Ļ —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä –Ĺ–į–Ņ–ł—Ā–į—ā—Ć, —á–Ķ–ľ –≤ —á—É–∂–ĺ–ľ —Ä–į–∑–Ī–ł—Ä–į—ā—Ć—Ā—Ź. –£–∂–Ķ —Ā–Ķ–Ļ—á–į—Ā –Ņ—Ä–ĺ—Ā—ā—č–Ķ –Ņ—Ä–ł–ľ–Ķ—Ä—č —ā–ł–Ņ–į —Ą–į–ļ—ā–ĺ—Ä–ł–į–Ľ–į –ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä—É—é—ā—Ā—Ź –≤ uf \ micro forth \ (–Ņ—Ä–ł –∂–Ķ–Ľ–į–Ĺ–ł–ł –ł –≤ –ļ–Ľ–į—Ā—Ā–ł—á–Ķ—Ā–ļ–ł–Ļ —Ą–ĺ—Ä—ā —ā—Ä–ł–≤–ł–į–Ľ—Ć–Ĺ–ĺ –ĺ—ā—ā—Ä–į–Ĺ—Ā–Ľ–ł—Ä—É—é—ā—Ā—Ź) –ł —Ä–į–Ī–ĺ—ā–į—é—ā, –Ĺ—É–∂–Ĺ–ĺ –Ľ–ł—ą—Ć —É—Ā–ł–Ľ–ł–Ķ, —á—ā–ĺ–Ī—č –∑–į—Ā—ā–į–≤–ł—ā—Ć —Ā–Ķ–Ī—Ź –ī–ĺ–≤–Ķ—Ā—ā–ł –ī–ĺ —É–ľ–į. –ź –ļ—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ, –Ľ—é–Ī–ĺ–Ļ —É–≤–į–∂–į—é—Č–ł–Ļ —Ā–Ķ–Ī—Ź –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä –ī–ĺ–Ľ–∂–Ķ–Ĺ —É–ľ–Ķ—ā—Ć –ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä–ĺ–≤–į—ā—Ć —Ā–į–ľ —Ā–Ķ–Ī—Ź, –Ņ–ĺ—ć—ā–ĺ–ľ—É –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź—ā–ĺ—Ä —Ā–ł –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ī—č—ā—Ć –Ĺ–į–Ņ–ł—Ā–į–Ĺ –Ĺ–į —Ā–ł (—Ź –Ņ–ĺ–ļ–į —Ā–į–ľ —Ā–Ķ–Ī—Ź –Ĺ–Ķ –ļ–ĺ–ľ–Ņ–ł–Ľ–ł—Ä—É—é, –Ņ–ĺ—ć—ā–ĺ–ľ—É –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ –Ĺ–į tcc –ī–Ķ–Ľ–į—é), –į duskos –ł cc64 –≤—Ä–ĺ–ī–Ķ –Ĺ–į —Ą–ĺ—Ä—ā–Ķ –Ĺ–į–Ņ–ł—Ā–į–Ĺ—č, –Ķ—Ā–Ľ–ł —Ź –Ņ—Ä–į–≤–ł–Ľ—Ć–Ĺ–ĺ –Ņ—É—ā–į—é. :)

tinytapeout - –ļ–Ľ–į—Ā—Ā–Ĺ–į—Ź –∑–į–ī—É–ľ–ļ–į, –Ĺ–ĺ —Ź –ī–ĺ —ā–į–ļ–ĺ–≥–ĺ –Ĺ–Ķ –ī–ĺ—Ä–ĺ—Ā –Ķ—Č–Ķ :)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –í—Ā —Ā–Ķ–Ĺ 24, 2023 13:31 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

Total Vacuum –Ņ–ł—Ā–į–Ľ(–į): –Ě–į–ī–ĺ –Ī—É–ī–Ķ—ā –ļ–į–ļ-–Ĺ–ł–Ī—É–ī—Ć —Ā–ĺ–Ī—Ä–į—ā—Ć—Ā—Ź –ł –Ĺ–į–Ņ–ł—Ā–į—ā—Ć —Ā–≤–ĺ–Ļ —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä —Ā–ł-–≤-—Ą–ĺ—Ä—ā, —á—ā–ĺ–Ī—č –Ĺ–į –ľ–ĺ–Ķ–ľ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ķ —Ā–ł-—ą–Ĺ—č–Ķ —ā–Ķ—Ā—ā—č –≥–ĺ–Ĺ—Ź—ā—Ć  –ú–ĺ–∂–Ĺ–ĺ –ĺ—ā—ā–ĺ–Ľ–ļ–Ĺ—É—ā—Ć—Ā—Ź –ĺ—ā —Ä–į–Ĺ–Ķ–Ķ–Ķ —É–∂–Ķ "—Ā–ī–Ķ–Ľ–į–Ĺ–Ĺ—č—Ö" –≤–į—Ä–ł–į–Ĺ—ā–ĺ–≤ (–ł –≤ —Ä–į–ľ–ļ–į—Ö –ĺ–Ī—Ā—É–∂–ī–Ķ–Ĺ–ł—Ź –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ c LCC -> Forth) –ł–Ľ–ł –Ņ–ĺ—Ź–≤–ł—ą–ł—Ö—Ā—Ź –ĺ—Ä–ł–≥–ł–Ĺ–į–Ľ—Ć–Ĺ—č—Ö –ļ–į–ļ –°–°64 –ł/–ł–Ľ–ł –≤—Ä–ĺ–ī–Ķ –≤ DuskOS –ł–Ľ–ł –∑–į–ī–Ķ–Ļ—Ā—ā–≤–ĺ–≤–į–į—ā—Ć –Ī–ł–Ī–Ľ–ł–ĺ—ā–Ķ–ļ–ł —Ā –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł—Ź–ľ–ł –Ņ–ĺ–ī–ĺ–Ī–Ĺ—č–Ķ LibJit. P.S. –ė–∑ —ā–ĺ–Ņ–ł–ļ–į –ó–į–ļ–į–∑ —Ā–ĺ–Ī—Ā—ā–≤–Ķ–Ĺ–Ĺ—č—Ö –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ —á–Ķ—Ä–Ķ–∑ TinyTapeout –ļ—ā–ĺ —ā–ĺ –∑–į–ļ–į–∑–į–Ľ –ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—É —Ā–≤–ĺ–Ķ–≥–ĺ –Ņ—Ä–ĺ–Ķ–ļ—ā–į —Ā RayCasting https://github.com/algofoogle/tt04-raybox-zerohttps://github.com/algofoogle/raybox-zero –ü—Ä–ł –∂–Ķ–Ľ–į–Ĺ–ł–ł, –≤–Ķ—Ä–ĺ—Ź—ā–Ĺ–ĺ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ, –ł –∑–į–ļ–į–∑–į—ā—Ć —Ā–≤–ĺ–Ļ –§–ĺ—Ä—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤ –ļ—Ä–Ķ–ľ–Ĺ–ł–ł –Ĺ–į –ł—Ā–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–Ķ –≤ —Ā–Ľ–Ķ–ī—É—é—Č–ł–Ļ TT05  [quote="Total Vacuum"]–Ě–į–ī–ĺ –Ī—É–ī–Ķ—ā –ļ–į–ļ-–Ĺ–ł–Ī—É–ī—Ć —Ā–ĺ–Ī—Ä–į—ā—Ć—Ā—Ź –ł –Ĺ–į–Ņ–ł—Ā–į—ā—Ć —Ā–≤–ĺ–Ļ —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä —Ā–ł-–≤-—Ą–ĺ—Ä—ā, —á—ā–ĺ–Ī—č –Ĺ–į –ľ–ĺ–Ķ–ľ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ķ —Ā–ł-—ą–Ĺ—č–Ķ —ā–Ķ—Ā—ā—č –≥–ĺ–Ĺ—Ź—ā—Ć :)[/quote]

–ú–ĺ–∂–Ĺ–ĺ –ĺ—ā—ā–ĺ–Ľ–ļ–Ĺ—É—ā—Ć—Ā—Ź –ĺ—ā —Ä–į–Ĺ–Ķ–Ķ–Ķ —É–∂–Ķ "—Ā–ī–Ķ–Ľ–į–Ĺ–Ĺ—č—Ö" –≤–į—Ä–ł–į–Ĺ—ā–ĺ–≤ (–ł –≤ —Ä–į–ľ–ļ–į—Ö –ĺ–Ī—Ā—É–∂–ī–Ķ–Ĺ–ł—Ź –Ĺ–į –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —Ą–ĺ—Ä—É–ľ–Ķ c LCC -> Forth) –ł–Ľ–ł –Ņ–ĺ—Ź–≤–ł—ą–ł—Ö—Ā—Ź –ĺ—Ä–ł–≥–ł–Ĺ–į–Ľ—Ć–Ĺ—č—Ö –ļ–į–ļ –°–°64 –ł/–ł–Ľ–ł –≤—Ä–ĺ–ī–Ķ –≤ DuskOS –ł–Ľ–ł –∑–į–ī–Ķ–Ļ—Ā—ā–≤–ĺ–≤–į–į—ā—Ć –Ī–ł–Ī–Ľ–ł–ĺ—ā–Ķ–ļ–ł —Ā –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł—Ź–ľ–ł –Ņ–ĺ–ī–ĺ–Ī–Ĺ—č–Ķ LibJit.

P.S. –ė–∑ —ā–ĺ–Ņ–ł–ļ–į [url=http://www.nedopc.org/forum/viewtopic.php?f=68&t=21972&start=15]–ó–į–ļ–į–∑ —Ā–ĺ–Ī—Ā—ā–≤–Ķ–Ĺ–Ĺ—č—Ö –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ —á–Ķ—Ä–Ķ–∑ TinyTapeout[/url] –ļ—ā–ĺ —ā–ĺ –∑–į–ļ–į–∑–į–Ľ –ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—É —Ā–≤–ĺ–Ķ–≥–ĺ –Ņ—Ä–ĺ–Ķ–ļ—ā–į —Ā RayCasting

https://github.com/algofoogle/tt04-raybox-zero

https://github.com/algofoogle/raybox-zero

[img]https://github.com/algofoogle/tt04-raybox-zero/raw/main/doc/fpga-vs-sim.jpg[/img]

–ü—Ä–ł –∂–Ķ–Ľ–į–Ĺ–ł–ł, –≤–Ķ—Ä–ĺ—Ź—ā–Ĺ–ĺ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ, –ł –∑–į–ļ–į–∑–į—ā—Ć —Ā–≤–ĺ–Ļ –§–ĺ—Ä—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤ –ļ—Ä–Ķ–ľ–Ĺ–ł–ł –Ĺ–į –ł—Ā–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–Ķ –≤ [url=https://github.com/TinyTapeout/tt05-submission-template]—Ā–Ľ–Ķ–ī—É—é—Č–ł–Ļ TT05[/url] :)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°–Ī —Ā–Ķ–Ĺ 09, 2023 12:49 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

KPG –Ņ–ł—Ā–į–Ľ(–į): –°—ā–į–Ĺ–ī–į—Ä—ā–Ĺ—č–Ļ C–ł —ā–Ķ—Ā—ā Coremark–Ě–į–ī–ĺ –Ī—É–ī–Ķ—ā –ļ–į–ļ-–Ĺ–ł–Ī—É–ī—Ć —Ā–ĺ–Ī—Ä–į—ā—Ć—Ā—Ź –ł –Ĺ–į–Ņ–ł—Ā–į—ā—Ć —Ā–≤–ĺ–Ļ —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä —Ā–ł-–≤-—Ą–ĺ—Ä—ā, —á—ā–ĺ–Ī—č –Ĺ–į –ľ–ĺ–Ķ–ľ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ķ —Ā–ł-—ą–Ĺ—č–Ķ —ā–Ķ—Ā—ā—č –≥–ĺ–Ĺ—Ź—ā—Ć  –ö—Ā—ā–į—ā–ł, –Ņ–ĺ–ī—É–ľ–į–Ľ–ĺ—Ā—Ć, —á—ā–ĺ –ł c 3-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł (—á—ā–ĺ–Ī—č —É—ā—Ä–į–ľ–Ī–ĺ–≤–į—ā—Ć 6 –ļ–ĺ–ľ–į–Ĺ–ī –≤ 18-–Ī–ł—ā–Ĺ–ĺ–ľ —Ā–Ľ–ĺ–≤–Ķ –ü–õ–ė–°) –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –≤–∑–Ľ–Ķ—ā–ł—ā. –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, —ā–į–ļ–ĺ–Ļ: –ö–ĺ–ī: 0 1 push @ ! jz nand - –õ–ł—ā–Ķ—Ä–į–Ľ—č –Ĺ–į–Ī–ł–≤–į—é—ā—Ā—Ź –Ņ—Ä–ł –Ņ–ĺ–ľ–ĺ—Č–ł –ļ–ĺ–ľ–į–Ĺ–ī—č push, –∑–į –ļ–ĺ—ā–ĺ—Ä–ĺ–Ļ —Ā–Ľ–Ķ–ī—É–Ķ—ā —Ā–Ķ—Ä–ł—Ź –ļ–ĺ–ľ–į–Ĺ–ī 0/1, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –ī–ĺ–Ņ–ł—Ā—č–≤–į—é—ā —Ā–Ņ—Ä–į–≤–į –Ĺ–ĺ–Ľ–ł–ļ –ł–Ľ–ł –Ķ–ī–ł–Ĺ–ł—á–ļ—É –≤ –ī–≤–ĺ–ł—á–Ĺ–ĺ–Ķ –Ņ—Ä–Ķ–ī—Ā—ā–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –≤–Ķ—Ä—ą–ł–Ĺ—č —Ā—ā–Ķ–ļ–į. –°—ā–Ķ–ļ –≤–ĺ–∑–≤—Ä–į—ā–ĺ–≤ –ī–Ķ–Ľ–į–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ–ĺ –Ĺ–į –Ī–į–∑–Ķ –ľ–į—Ā—Ā–ł–≤–į. –°—ā–Ķ–ļ–ĺ–≤—č–Ķ –ľ–į–Ĺ–ł–Ņ—É–Ľ—Ź—Ü–ł–ł - —á–Ķ—Ä–Ķ–∑ –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–Ķ –Ņ–Ķ—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–Ķ –≤ —Ā–Ķ–≥–ľ–Ķ–Ĺ—ā–Ķ –ī–į–Ĺ–Ĺ—č—Ö. –Ę–į–ļ–ĺ–Ļ —Ā–≤–ĺ–Ķ–ĺ–Ī—Ä–į–∑–Ĺ—č–Ļ —Ā—ā–Ķ–ļ–ĺ–≤—č–Ļ brainfuck –Ņ–ĺ–Ľ—É—á–į–Ķ—ā—Ā—Ź.  –Ě—É –ł–Ľ–ł —á—É—ā—Ć –Ī–ĺ–Ľ–Ķ–Ķ –Ņ—Ä–ĺ–ī–≤–ł–Ĺ—É—ā–ĺ–Ķ: –ö–ĺ–ī: call ret word @ ! jz nand - –ó–ī–Ķ—Ā—Ć –Ņ–ĺ–Ľ–Ĺ–ĺ—Ü–Ķ–Ĺ–Ĺ—č–Ķ call/ret, –į word –Ņ–Ķ—Ä–Ķ–ļ–Ľ—é—á–į–Ķ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤ —Ä–Ķ–∂–ł–ľ –≤–≤–ĺ–ī–į –Ľ–ł—ā–Ķ—Ä–į–Ľ–ĺ–≤ –Ĺ–į –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —ā–į–ļ—ā–ĺ–≤. –Ě–ĺ –≤—Ā–Ķ —ć—ā–ĺ –ľ–ĺ–∂–Ķ—ā –ł–ľ–Ķ—ā—Ć —Ö–ĺ—ā—Ć –ļ–į–ļ–ĺ–Ļ-—ā–ĺ —Ā–ľ—č—Ā–Ľ —ā–ĺ–Ľ—Ć–ļ–ĺ –≤ —ā–ĺ–ľ —Ā–Ľ—É—á–į–Ķ, –Ķ—Ā–Ľ–ł —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł—Ź –≤ —á–į—Ā—ā–ł –Ņ–ĺ—ā—Ä–Ķ–Ī–Ľ–Ķ–Ĺ–ł—Ź —Ä–Ķ—Ā—É—Ä—Ā–ĺ–≤ –ü–õ–ė–° –ĺ–ļ–į–∂–Ķ—ā—Ā—Ź –≤ —Ä–į–∑—č –Ī–ĺ–Ľ–Ķ–Ķ –ļ–ĺ–ľ–Ņ–į–ļ—ā–Ĺ–ĺ–Ļ, —á–Ķ–ľ –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł, –į –ł–Ĺ–į—á–Ķ –ĺ–≤—á–ł–Ĺ–ļ–į –ł –ī–į–Ľ–Ķ–Ķ –Ņ–ĺ —ā–Ķ–ļ—Ā—ā—É  –ē—Ā–Ľ–ł –Ņ–ĺ–Ľ—É—á–ł—ā—Ā—Ź –ļ–ĺ–ľ–Ņ–į–ļ—ā–Ĺ–ĺ–Ķ, —ā–ĺ–≥–ī–į –ľ–ĺ–∂–Ĺ–ĺ –Ī—É–ī–Ķ—ā –≤—ā–ł—Ā–Ĺ—É—ā—Ć –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —ā—É–ī–į, –≥–ī–Ķ –ľ–Ķ—Ā—ā–į –Ņ–ĺ—á—ā–ł –Ĺ–Ķ –ĺ—Ā—ā–į–Ľ–ĺ—Ā—Ć. –Ě—É –ł–Ľ–ł –ļ—É—á—É —Ź–ī–Ķ—Ä –≤ –ü–õ–ė–° –∑–į–Ņ–ł—Ö–Ĺ—É—ā—Ć, –ĺ—Ā–ĺ–Ī–Ķ–Ĺ–Ĺ–ĺ –Ķ—Ā–Ľ–ł —É–ľ–Ĺ–ĺ–∂–Ķ–Ĺ–ł—Ź –≤ —Ā–ł—Ā—ā–Ķ–ľ–Ķ –ļ–ĺ–ľ–į–Ĺ–ī –Ĺ–Ķ –Ī—É–ī–Ķ—ā. –Ě—É –į –Ņ–ĺ —Ö–ĺ—Ä–ĺ—ą–Ķ–ľ—É –Ĺ–į–ī–ĺ –Ī—č —É–∂–Ķ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —Ā 6-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł –≤—č–ļ–į—ā—č–≤–į—ā—Ć: –ī–į–∂–Ķ –≤ –Ņ—Ä–ĺ—Ā—ā–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ –Ī–Ķ–∑ –į–ļ—Ā–Ķ–Ľ–Ķ—Ä–į—ā–ĺ—Ä–į (–Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī –∑–į —ā–į–ļ—ā) –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ĺ–Ķ —Ā–ł–Ľ—Ć–Ĺ–ĺ —É—Ā—ā—É–Ņ–į—ā—Ć —Ä–į—Ā–ļ–ĺ—á–Ķ–≥–į—Ä–Ķ–Ĺ–Ĺ–ĺ–ľ—É –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł.  [quote="KPG"]–°—ā–į–Ĺ–ī–į—Ä—ā–Ĺ—č–Ļ C–ł —ā–Ķ—Ā—ā [url=https://github.com/eembc/coremark]Coremark[/url][/quote]–Ě–į–ī–ĺ –Ī—É–ī–Ķ—ā –ļ–į–ļ-–Ĺ–ł–Ī—É–ī—Ć —Ā–ĺ–Ī—Ä–į—ā—Ć—Ā—Ź –ł –Ĺ–į–Ņ–ł—Ā–į—ā—Ć —Ā–≤–ĺ–Ļ —ā—Ä–į–Ĺ—Ā–Ľ—Ź—ā–ĺ—Ä —Ā–ł-–≤-—Ą–ĺ—Ä—ā, —á—ā–ĺ–Ī—č –Ĺ–į –ľ–ĺ–Ķ–ľ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ķ —Ā–ł-—ą–Ĺ—č–Ķ —ā–Ķ—Ā—ā—č –≥–ĺ–Ĺ—Ź—ā—Ć :)

–ö—Ā—ā–į—ā–ł, –Ņ–ĺ–ī—É–ľ–į–Ľ–ĺ—Ā—Ć, —á—ā–ĺ –ł c 3-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł (—á—ā–ĺ–Ī—č —É—ā—Ä–į–ľ–Ī–ĺ–≤–į—ā—Ć 6 –ļ–ĺ–ľ–į–Ĺ–ī –≤ 18-–Ī–ł—ā–Ĺ–ĺ–ľ —Ā–Ľ–ĺ–≤–Ķ –ü–õ–ė–°) –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤–Ņ–ĺ–Ľ–Ĺ–Ķ –≤–∑–Ľ–Ķ—ā–ł—ā. –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä, —ā–į–ļ–ĺ–Ļ:[code]0 1 push @ ! jz nand -[/code]–õ–ł—ā–Ķ—Ä–į–Ľ—č –Ĺ–į–Ī–ł–≤–į—é—ā—Ā—Ź –Ņ—Ä–ł –Ņ–ĺ–ľ–ĺ—Č–ł –ļ–ĺ–ľ–į–Ĺ–ī—č push, –∑–į –ļ–ĺ—ā–ĺ—Ä–ĺ–Ļ —Ā–Ľ–Ķ–ī—É–Ķ—ā —Ā–Ķ—Ä–ł—Ź –ļ–ĺ–ľ–į–Ĺ–ī 0/1, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –ī–ĺ–Ņ–ł—Ā—č–≤–į—é—ā —Ā–Ņ—Ä–į–≤–į –Ĺ–ĺ–Ľ–ł–ļ –ł–Ľ–ł –Ķ–ī–ł–Ĺ–ł—á–ļ—É –≤ –ī–≤–ĺ–ł—á–Ĺ–ĺ–Ķ –Ņ—Ä–Ķ–ī—Ā—ā–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –≤–Ķ—Ä—ą–ł–Ĺ—č —Ā—ā–Ķ–ļ–į. –°—ā–Ķ–ļ –≤–ĺ–∑–≤—Ä–į—ā–ĺ–≤ –ī–Ķ–Ľ–į–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ–ĺ –Ĺ–į –Ī–į–∑–Ķ –ľ–į—Ā—Ā–ł–≤–į. –°—ā–Ķ–ļ–ĺ–≤—č–Ķ –ľ–į–Ĺ–ł–Ņ—É–Ľ—Ź—Ü–ł–ł - —á–Ķ—Ä–Ķ–∑ –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–Ķ –Ņ–Ķ—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–Ķ –≤ —Ā–Ķ–≥–ľ–Ķ–Ĺ—ā–Ķ –ī–į–Ĺ–Ĺ—č—Ö. –Ę–į–ļ–ĺ–Ļ —Ā–≤–ĺ–Ķ–ĺ–Ī—Ä–į–∑–Ĺ—č–Ļ —Ā—ā–Ķ–ļ–ĺ–≤—č–Ļ brainfuck –Ņ–ĺ–Ľ—É—á–į–Ķ—ā—Ā—Ź. :)

–Ě—É –ł–Ľ–ł —á—É—ā—Ć –Ī–ĺ–Ľ–Ķ–Ķ –Ņ—Ä–ĺ–ī–≤–ł–Ĺ—É—ā–ĺ–Ķ:[code]call ret word @ ! jz nand -[/code]–ó–ī–Ķ—Ā—Ć –Ņ–ĺ–Ľ–Ĺ–ĺ—Ü–Ķ–Ĺ–Ĺ—č–Ķ call/ret, –į word –Ņ–Ķ—Ä–Ķ–ļ–Ľ—é—á–į–Ķ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤ —Ä–Ķ–∂–ł–ľ –≤–≤–ĺ–ī–į –Ľ–ł—ā–Ķ—Ä–į–Ľ–ĺ–≤ –Ĺ–į –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —ā–į–ļ—ā–ĺ–≤.

–Ě–ĺ –≤—Ā–Ķ —ć—ā–ĺ –ľ–ĺ–∂–Ķ—ā –ł–ľ–Ķ—ā—Ć —Ö–ĺ—ā—Ć –ļ–į–ļ–ĺ–Ļ-—ā–ĺ —Ā–ľ—č—Ā–Ľ —ā–ĺ–Ľ—Ć–ļ–ĺ –≤ —ā–ĺ–ľ —Ā–Ľ—É—á–į–Ķ, –Ķ—Ā–Ľ–ł —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł—Ź –≤ —á–į—Ā—ā–ł –Ņ–ĺ—ā—Ä–Ķ–Ī–Ľ–Ķ–Ĺ–ł—Ź —Ä–Ķ—Ā—É—Ä—Ā–ĺ–≤ –ü–õ–ė–° –ĺ–ļ–į–∂–Ķ—ā—Ā—Ź –≤ —Ä–į–∑—č –Ī–ĺ–Ľ–Ķ–Ķ –ļ–ĺ–ľ–Ņ–į–ļ—ā–Ĺ–ĺ–Ļ, —á–Ķ–ľ –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł, –į –ł–Ĺ–į—á–Ķ –ĺ–≤—á–ł–Ĺ–ļ–į –ł –ī–į–Ľ–Ķ–Ķ –Ņ–ĺ —ā–Ķ–ļ—Ā—ā—É :) –ē—Ā–Ľ–ł –Ņ–ĺ–Ľ—É—á–ł—ā—Ā—Ź –ļ–ĺ–ľ–Ņ–į–ļ—ā–Ĺ–ĺ–Ķ, —ā–ĺ–≥–ī–į –ľ–ĺ–∂–Ĺ–ĺ –Ī—É–ī–Ķ—ā –≤—ā–ł—Ā–Ĺ—É—ā—Ć –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —ā—É–ī–į, –≥–ī–Ķ –ľ–Ķ—Ā—ā–į –Ņ–ĺ—á—ā–ł –Ĺ–Ķ –ĺ—Ā—ā–į–Ľ–ĺ—Ā—Ć. –Ě—É –ł–Ľ–ł –ļ—É—á—É —Ź–ī–Ķ—Ä –≤ –ü–õ–ė–° –∑–į–Ņ–ł—Ö–Ĺ—É—ā—Ć, –ĺ—Ā–ĺ–Ī–Ķ–Ĺ–Ĺ–ĺ –Ķ—Ā–Ľ–ł —É–ľ–Ĺ–ĺ–∂–Ķ–Ĺ–ł—Ź –≤ —Ā–ł—Ā—ā–Ķ–ľ–Ķ –ļ–ĺ–ľ–į–Ĺ–ī –Ĺ–Ķ –Ī—É–ī–Ķ—ā.

–Ě—É –į –Ņ–ĺ —Ö–ĺ—Ä–ĺ—ą–Ķ–ľ—É –Ĺ–į–ī–ĺ –Ī—č —É–∂–Ķ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —Ā 6-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł –≤—č–ļ–į—ā—č–≤–į—ā—Ć: –ī–į–∂–Ķ –≤ –Ņ—Ä–ĺ—Ā—ā–ĺ–ľ –≤–į—Ä–ł–į–Ĺ—ā–Ķ –Ī–Ķ–∑ –į–ļ—Ā–Ķ–Ľ–Ķ—Ä–į—ā–ĺ—Ä–į (–Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī –∑–į —ā–į–ļ—ā) –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ĺ–Ķ —Ā–ł–Ľ—Ć–Ĺ–ĺ —É—Ā—ā—É–Ņ–į—ā—Ć —Ä–į—Ā–ļ–ĺ—á–Ķ–≥–į—Ä–Ķ–Ĺ–Ĺ–ĺ–ľ—É –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É —Ā 4-–Ī–ł—ā–Ĺ—č–ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ–ł. :)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°—Ä —Ā–Ķ–Ĺ 06, 2023 22:14 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

–ß—ā–ĺ –∂, –Ņ—Ä–ĺ–ī–ĺ–Ľ–∂–ł–ľ...  –ė–ľ–Ķ–Ķ—ā—Ā—Ź —Ā–ł—Ā—ā–Ķ–ľ–į –ļ–ĺ–ľ–į–Ĺ–ī –ö–ĺ–ī: xxx xxx xxx abs word jz call ret @ ! dec dup inc - + jnz –ł —Ä–į—Ā–ļ–ĺ—á–Ķ–≥–į—Ä–Ķ–Ĺ–Ĺ—č–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, –ļ–ĺ—ā–ĺ—Ä—č–Ļ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –∑–į —ā–į–ļ—ā –ö–ĺ–ī: n

n call

n jz

n +

n -

n @ \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n ! \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n inc \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n dec \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n abs –ü—Ä–ĺ–ł–≥—Ä—č—ą ARM –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ "—ć–ľ—É–Ľ—Ź—Ü–ł–ł" —Ā–ĺ—Ā—ā–į–≤–Ľ—Ź–Ķ—ā 1.17 —Ä–į–∑. –Ē–į–Ľ–Ķ–Ķ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ –ī–Ķ–Ľ–į–Ķ–ľ –∑–į —ā–į–ļ—ā: –ö–ĺ–ī: n @ @ \ –Ņ—Ä–ĺ–ł–≥—Ä—č—ą –≤ 1.11 —Ä–į–∑

- dup \ –Ņ—Ä–ĺ–ł–≥—Ä—č—ą –≤ 1.04 —Ä–į–∑–į –ė, –Ĺ–į–ļ–ĺ–Ĺ–Ķ—Ü –ö–ĺ–ī: - - \ –Ņ—Ä–ĺ–ł–≥—Ä—č—ą –≤ 0.98 —Ä–į–∑! –ź —ć—ā–ĺ –ĺ–∑–Ĺ–į—á–į–Ķ—ā, —á—ā–ĺ —É–∂–Ķ –Ņ—Ä–ĺ—Ü–Ķ–Ĺ—ā–į –Ĺ–į 2 –ĺ–Ī–≥–ĺ–Ĺ—Ź–Ķ–ľ ARM, —á—ā–ĺ –ł —ā—Ä–Ķ–Ī–ĺ–≤–į–Ľ–ĺ—Ā—Ć –ī–ĺ–ļ–į–∑–į—ā—Ć!  –ü—Ä–ł—á–Ķ–ľ, –Ķ—Ā–Ľ–ł –Ņ–ĺ—Ā–ľ–ĺ—ā—Ä–Ķ—ā—Ć –Ĺ–į –ļ–ĺ–ī (—Ā–≥—Ä—É–Ņ–Ņ–ł—Ä–ĺ–≤–į–Ĺ—č 4-–Ī–ł—ā–Ĺ—č–Ķ –ļ–ĺ–ľ–į–Ĺ–ī—č, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –∑–į —ā–į–ļ—ā) –ö–ĺ–ī: 40000 400099 [2] 0 r1 ! [1] MOV R1,#0

40000 4000D9 [2] 0 r0 ! [1] MOV R0,#0

40000 4000B9 [2] 0 r6 ! [1] MOV R6,#0

[ ] `: line40` [ ] LINE40:

400098 40008D [2] r1 @ r3 - [1] CMP R1,R3

400D05 [1] `line180` jz [3] BEQ LINE180

4000B8 400098 9 [3] r6 @ r1 @ ! [?] STR R6,[SP,R1,LSL #2]

40009C [1] r1 inc [1] ADD R1,R1,#1

40008 4000B9 [2] r3 r6 ! [1] MOV R6,R3

[ ] `: line70` [ ] LINE70:

4000DC [1] r0 inc [1] ADD R0,R0,#1

400098 4000A9 [2] r1 @ r2 ! [1] MOV R2,R1

[ ] `: line90` [ ] LINE90:

4000AA [1] r2 dec [1] SUBS R2,R2,#1

400285 [1] `line40` jz [3] BEQ LINE40

[ ] [?] LDR R7,[SP,R2,LSL #2]

4000B8 4000A88 DB 4000C9 [4] r6 @ r2 @ @ - dup r7 ! [1] SUBS R7,R6,R7

400AB5 [1] `line140` jz [3] BEQ LINE140

4000C3 [1] r7 abs [1] RSBMI R7,R7,#0

400098 4000A8 DD [3] r1 @ r2 @ - - [1] SUB R8,R1,R2

[ ] [1] CMP R7,R8

4006AF [1] `line90` jnz [3] BNE LINE90

[ ] `: line140` [ ] LINE140:

4000BA [1] r6 dec [1] SUBS R6,R6,#1

40058F [1] `line70` jnz [3] BNE LINE70

40009A [1] r1 dec [1] SUBS R1,R1,#1

4000988 4000B9 [2] r1 @ @ r6 ! [?] LDR R6,[SP,R1,LSL #2]

400ABF [1] `line140` jnz [3] BNE LINE140

[ ] `: line180` [ ] LINE180: , —ā–ĺ –≤–ł–ī–Ĺ–ĺ –Ķ—Č–Ķ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –ľ–Ķ—Ā—ā, –≥–ī–Ķ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ—č –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–ł, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, n @ ! –ī–Ľ—Ź –ļ–ĺ—Ä–ĺ—ā–ļ–ł—Ö –į–ī—Ä–Ķ—Ā–ĺ–≤ –∑–į —ā–į–ļ—ā –ł–Ľ–ł –ī–į–∂–Ķ —ć–ļ–∑–ĺ—ā–ł–ļ–į –≤—Ä–ĺ–ī–Ķ n @ @ - dup –ł–Ľ–ł n @ - -, –Ĺ–ĺ, –ī—É–ľ–į—é, –Ņ–ĺ—Ä–į –ĺ—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć—Ā—Ź, –ł–Ī–ĺ ARM —É–∂–Ķ –Ņ–ĺ–≤–Ķ—Ä–∂–Ķ–Ĺ, –Ņ—Ä–ł—á–Ķ–ľ –Ĺ–į –Ķ–≥–ĺ –Ņ–ĺ–Ľ–Ķ –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ —ć–ľ—É–Ľ—Ź—Ü–ł–ł  –ö—Ā—ā–į—ā–ł, –Ķ—Ā–Ľ–ł –Ī—Ä–į—ā—Ć —Ā–į–ľ—č–Ļ —Ā–≤–Ķ–∂–ł–Ļ 4-–Ī–ł—ā–Ĺ—č–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, —ā–ĺ –ī–į–∂–Ķ –≤ —Ā–į–ľ–ĺ–ľ –Ņ—Ä–ĺ—Ā—ā–ĺ–ľ –ł—Ā–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–ł –ĺ–Ĺ —É—Ā—ā—É–Ņ–į–Ķ—ā ARM –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ —ć–ľ—É–Ľ—Ź—Ü–ł–ł –≤ 5 —Ā —á–Ķ–ľ-—ā–ĺ —Ä–į–∑. –° –ī—Ä—É–≥–ĺ–Ļ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č, ARM –Ņ—Ä–ł —Ä–ł—Ā–ĺ–≤–į–Ĺ–ł–ł 3d-–Ī—Ä–ĺ–ī–ł–Ľ–ļ–ł (–Ņ–ĺ —Ā—É—ā–ł —ć—ā–ĺ —Ä–Ķ–∂–ł–ľ —ć–ľ—É–Ľ—Ź—Ü–ł–ł —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į!) –≤ —Ā–≤–ĺ—é –ĺ—á–Ķ—Ä–Ķ–ī—Ć —Ā–į–ľ —É—Ā—ā—É–Ņ–į–Ķ—ā —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É –≤ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —Ä–į–∑. –Ě—É –į –Ņ—Ä–ĺ–ī–≤–ł–Ĺ—É—ā—č–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ī–Ķ–∑ –Ņ—Ä–ĺ–Ī–Ľ–Ķ–ľ –ī–ĺ–≥–ĺ–Ĺ—Ź–Ķ—ā ARM –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ —ć–ľ—É–Ľ—Ź—Ü–ł–ł, –ĺ–Ī–≥–ĺ–Ĺ—Ź—Ź –Ņ—Ä–ł —ć—ā–ĺ–ľ –≤ 10-20 –ł –Ī–ĺ–Ľ–Ķ–Ķ —Ä–į–∑ –Ņ—Ä–ł —Ä–ł—Ā–ĺ–≤–į–Ĺ–ł–ł 3d-–Ī—Ä–ĺ–ī–ł–Ľ–ļ–ł. –ü–ĺ–ī–ĺ–∑—Ä–Ķ–≤–į—é, —á—ā–ĺ —Ö–ł—Č–Ĺ—č–Ķ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —É–ī–Ķ–Ľ–į—é—ā ARM –ĺ–ī–Ĺ–ĺ–Ļ –Ľ–Ķ–≤–ĺ–Ļ  –ö—Ā—ā–į—ā–ł, –Ņ–ĺ—Ā–Ľ–Ķ–ī–Ĺ–ł–Ļ —Ā—É—Ä—Ä–ĺ–≥–į—ā–Ĺ—č–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ł–∑ —ā–Ķ—Ā—ā–į n-queens –Ņ—Ä–ł —á–į—Ā—ā–ĺ—ā–Ķ 50MHz –≤—č–ī–į–Ķ—ā –ľ–Ķ–į–Ĺ–ī—Ä 7.14MHz –Ĺ–į —ā–Ķ—Ā—ā–Ķ blink –ö–ĺ–ī: :: begin (( ;

:: again )) ;

:: GPIO 0x8000 ;

begin

0 GPIO !

1 GPIO !

again –ß—ā–ĺ –∂, –Ņ—Ä–ĺ–ī–ĺ–Ľ–∂–ł–ľ... :)

–ė–ľ–Ķ–Ķ—ā—Ā—Ź —Ā–ł—Ā—ā–Ķ–ľ–į –ļ–ĺ–ľ–į–Ĺ–ī[code]xxx xxx xxx abs word jz call ret @ ! dec dup inc - + jnz[/code] –ł —Ä–į—Ā–ļ–ĺ—á–Ķ–≥–į—Ä–Ķ–Ĺ–Ĺ—č–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, –ļ–ĺ—ā–ĺ—Ä—č–Ļ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –∑–į —ā–į–ļ—ā[code]n

n call

n jz

n +

n -

n @ \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n ! \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n inc \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n dec \ –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–ĺ–≤ 0-15

n abs[/code]–ü—Ä–ĺ–ł–≥—Ä—č—ą ARM –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ "—ć–ľ—É–Ľ—Ź—Ü–ł–ł" —Ā–ĺ—Ā—ā–į–≤–Ľ—Ź–Ķ—ā 1.17 —Ä–į–∑.

–Ē–į–Ľ–Ķ–Ķ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ –ī–Ķ–Ľ–į–Ķ–ľ –∑–į —ā–į–ļ—ā:[code]n @ @ \ –Ņ—Ä–ĺ–ł–≥—Ä—č—ą –≤ 1.11 —Ä–į–∑

- dup \ –Ņ—Ä–ĺ–ł–≥—Ä—č—ą –≤ 1.04 —Ä–į–∑–į[/code]–ė, –Ĺ–į–ļ–ĺ–Ĺ–Ķ—Ü

[code]- - \ –Ņ—Ä–ĺ–ł–≥—Ä—č—ą –≤ 0.98 —Ä–į–∑![/code]–ź —ć—ā–ĺ –ĺ–∑–Ĺ–į—á–į–Ķ—ā, —á—ā–ĺ —É–∂–Ķ –Ņ—Ä–ĺ—Ü–Ķ–Ĺ—ā–į –Ĺ–į 2 –ĺ–Ī–≥–ĺ–Ĺ—Ź–Ķ–ľ ARM, —á—ā–ĺ –ł —ā—Ä–Ķ–Ī–ĺ–≤–į–Ľ–ĺ—Ā—Ć –ī–ĺ–ļ–į–∑–į—ā—Ć! :) –ü—Ä–ł—á–Ķ–ľ, –Ķ—Ā–Ľ–ł –Ņ–ĺ—Ā–ľ–ĺ—ā—Ä–Ķ—ā—Ć –Ĺ–į –ļ–ĺ–ī (—Ā–≥—Ä—É–Ņ–Ņ–ł—Ä–ĺ–≤–į–Ĺ—č 4-–Ī–ł—ā–Ĺ—č–Ķ –ļ–ĺ–ľ–į–Ĺ–ī—č, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –∑–į —ā–į–ļ—ā)[code]40000 400099 [2] 0 r1 ! [1] MOV R1,#0

40000 4000D9 [2] 0 r0 ! [1] MOV R0,#0

40000 4000B9 [2] 0 r6 ! [1] MOV R6,#0

[ ] `: line40` [ ] LINE40:

400098 40008D [2] r1 @ r3 - [1] CMP R1,R3

400D05 [1] `line180` jz [3] BEQ LINE180

4000B8 400098 9 [3] r6 @ r1 @ ! [?] STR R6,[SP,R1,LSL #2]

40009C [1] r1 inc [1] ADD R1,R1,#1

40008 4000B9 [2] r3 r6 ! [1] MOV R6,R3

[ ] `: line70` [ ] LINE70:

4000DC [1] r0 inc [1] ADD R0,R0,#1

400098 4000A9 [2] r1 @ r2 ! [1] MOV R2,R1

[ ] `: line90` [ ] LINE90:

4000AA [1] r2 dec [1] SUBS R2,R2,#1

400285 [1] `line40` jz [3] BEQ LINE40

[ ] [?] LDR R7,[SP,R2,LSL #2]

4000B8 4000A88 DB 4000C9 [4] r6 @ r2 @ @ - dup r7 ! [1] SUBS R7,R6,R7

400AB5 [1] `line140` jz [3] BEQ LINE140

4000C3 [1] r7 abs [1] RSBMI R7,R7,#0

400098 4000A8 DD [3] r1 @ r2 @ - - [1] SUB R8,R1,R2

[ ] [1] CMP R7,R8

4006AF [1] `line90` jnz [3] BNE LINE90

[ ] `: line140` [ ] LINE140:

4000BA [1] r6 dec [1] SUBS R6,R6,#1

40058F [1] `line70` jnz [3] BNE LINE70

40009A [1] r1 dec [1] SUBS R1,R1,#1

4000988 4000B9 [2] r1 @ @ r6 ! [?] LDR R6,[SP,R1,LSL #2]

400ABF [1] `line140` jnz [3] BNE LINE140

[ ] `: line180` [ ] LINE180:[/code], —ā–ĺ –≤–ł–ī–Ĺ–ĺ –Ķ—Č–Ķ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –ľ–Ķ—Ā—ā, –≥–ī–Ķ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ—č –ĺ–Ņ—ā–ł–ľ–ł–∑–į—Ü–ł–ł, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, n @ ! –ī–Ľ—Ź –ļ–ĺ—Ä–ĺ—ā–ļ–ł—Ö –į–ī—Ä–Ķ—Ā–ĺ–≤ –∑–į —ā–į–ļ—ā –ł–Ľ–ł –ī–į–∂–Ķ —ć–ļ–∑–ĺ—ā–ł–ļ–į –≤—Ä–ĺ–ī–Ķ n @ @ - dup –ł–Ľ–ł n @ - -, –Ĺ–ĺ, –ī—É–ľ–į—é, –Ņ–ĺ—Ä–į –ĺ—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć—Ā—Ź, –ł–Ī–ĺ ARM —É–∂–Ķ –Ņ–ĺ–≤–Ķ—Ä–∂–Ķ–Ĺ, –Ņ—Ä–ł—á–Ķ–ľ –Ĺ–į –Ķ–≥–ĺ –Ņ–ĺ–Ľ–Ķ –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ —ć–ľ—É–Ľ—Ź—Ü–ł–ł :)

–ö—Ā—ā–į—ā–ł, –Ķ—Ā–Ľ–ł –Ī—Ä–į—ā—Ć —Ā–į–ľ—č–Ļ —Ā–≤–Ķ–∂–ł–Ļ 4-–Ī–ł—ā–Ĺ—č–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, —ā–ĺ –ī–į–∂–Ķ –≤ —Ā–į–ľ–ĺ–ľ –Ņ—Ä–ĺ—Ā—ā–ĺ–ľ –ł—Ā–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–ł –ĺ–Ĺ —É—Ā—ā—É–Ņ–į–Ķ—ā ARM –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ —ć–ľ—É–Ľ—Ź—Ü–ł–ł –≤ 5 —Ā —á–Ķ–ľ-—ā–ĺ —Ä–į–∑. –° –ī—Ä—É–≥–ĺ–Ļ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č, ARM –Ņ—Ä–ł —Ä–ł—Ā–ĺ–≤–į–Ĺ–ł–ł 3d-–Ī—Ä–ĺ–ī–ł–Ľ–ļ–ł (–Ņ–ĺ —Ā—É—ā–ł —ć—ā–ĺ —Ä–Ķ–∂–ł–ľ —ć–ľ—É–Ľ—Ź—Ü–ł–ł —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į!) –≤ —Ā–≤–ĺ—é –ĺ—á–Ķ—Ä–Ķ–ī—Ć —Ā–į–ľ —É—Ā—ā—É–Ņ–į–Ķ—ā —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É –≤ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —Ä–į–∑. –Ě—É –į –Ņ—Ä–ĺ–ī–≤–ł–Ĺ—É—ā—č–Ļ —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ī–Ķ–∑ –Ņ—Ä–ĺ–Ī–Ľ–Ķ–ľ –ī–ĺ–≥–ĺ–Ĺ—Ź–Ķ—ā ARM –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ķ–≥–ĺ —ć–ľ—É–Ľ—Ź—Ü–ł–ł, –ĺ–Ī–≥–ĺ–Ĺ—Ź—Ź –Ņ—Ä–ł —ć—ā–ĺ–ľ –≤ 10-20 –ł –Ī–ĺ–Ľ–Ķ–Ķ —Ä–į–∑ –Ņ—Ä–ł —Ä–ł—Ā–ĺ–≤–į–Ĺ–ł–ł 3d-–Ī—Ä–ĺ–ī–ł–Ľ–ļ–ł. –ü–ĺ–ī–ĺ–∑—Ä–Ķ–≤–į—é, —á—ā–ĺ —Ö–ł—Č–Ĺ—č–Ķ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—č —É–ī–Ķ–Ľ–į—é—ā ARM –ĺ–ī–Ĺ–ĺ–Ļ –Ľ–Ķ–≤–ĺ–Ļ :D

–ö—Ā—ā–į—ā–ł, –Ņ–ĺ—Ā–Ľ–Ķ–ī–Ĺ–ł–Ļ —Ā—É—Ä—Ä–ĺ–≥–į—ā–Ĺ—č–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ł–∑ —ā–Ķ—Ā—ā–į n-queens –Ņ—Ä–ł —á–į—Ā—ā–ĺ—ā–Ķ 50MHz –≤—č–ī–į–Ķ—ā –ľ–Ķ–į–Ĺ–ī—Ä 7.14MHz –Ĺ–į —ā–Ķ—Ā—ā–Ķ blink[code]:: begin (( ;

:: again )) ;

:: GPIO 0x8000 ;

begin

0 GPIO !

1 GPIO !

again[/code]

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –°—Ä —Ā–Ķ–Ĺ 06, 2023 21:53 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

Total Vacuum –Ņ–ł—Ā–į–Ľ(–į): –≠—ā–ĺ –Ĺ–Ķ –Ņ—Ä–Ķ–ī–Ķ–Ľ, –Ī—É–ī–Ķ—ā –Ľ—É—á—ą–Ķ  –°—ā–į–Ĺ–ī–į—Ä—ā–Ĺ—č–Ļ C–ł —ā–Ķ—Ā—ā Coremark (–ī–Ľ—Ź Forth —ā–ĺ–∂–Ķ –Ī—č–Ľ –Ņ–Ķ—Ä–Ķ–Ĺ–Ķ—Ā—Ď–Ĺ –ł –Ī—č–Ľ–ł –ł–∑–ľ–Ķ—Ä–Ķ–Ĺ–ł—Ź –≤ –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —ā–ĺ–Ņ–ł–ļ–Ķ –Ď–Ķ–Ĺ—á–ľ–į—Ä–ļ–į –§–ĺ—Ä—ā —Ā–ł—Ā—ā–Ķ–ľ) P.S. –Ę–į–Ī–Ľ–ł—Ü–į –Ĺ–į —Ā–į–Ļ—ā–Ķ –ł–∑–ľ–Ķ—Ä–Ķ–Ĺ–ł—Ź –ī–Ľ—Ź —Ä–į–∑–Ĺ—č—Ö –ļ—Ä–ł—Ā—ā–į–Ľ–ĺ–≤ https://www.eembc.org/coremark/scores.php–ö–ĺ–≥–ī–į —ā–ĺ –≤ —ć—ā–ĺ–ľ –Ď–Ķ–Ĺ—á–Ķ –Ī—č–Ľ–ł –ł –ī–į–Ĺ–Ĺ—č–Ķ –Ņ–ĺ —Ā—ā–Ķ–ļ–ĺ–≤–ĺ–ľ—É –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É PSC1000 Ignite.pdf (–ĺ—ā Patriot Scientific) igniteIP_20050506.pdf(0,13 –ľ–ł–ļ—Ä–ĺ–Ĺ 600–ú–ď—Ü) –Ē–Ľ—Ź PSC1000 Ignite –Ī—č–Ľ –ł –°–ł –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź–ĺ—Ä –ī–Ľ—Ź Win/Linux (–≤ –í–Ķ–Ī –į—Ä—Ö–ł–≤–Ķ –ĺ—ā 2003–≥ –Ĺ–Ķ —Ā–ĺ—Ö—Ä–į–Ĺ–Ķ–Ĺ—č) [quote="Total Vacuum"]–≠—ā–ĺ –Ĺ–Ķ –Ņ—Ä–Ķ–ī–Ķ–Ľ, –Ī—É–ī–Ķ—ā –Ľ—É—á—ą–Ķ :)[/quote]

–°—ā–į–Ĺ–ī–į—Ä—ā–Ĺ—č–Ļ C–ł —ā–Ķ—Ā—ā [url=https://github.com/eembc/coremark]Coremark[/url]

(–ī–Ľ—Ź Forth —ā–ĺ–∂–Ķ –Ī—č–Ľ –Ņ–Ķ—Ä–Ķ–Ĺ–Ķ—Ā—Ď–Ĺ –ł –Ī—č–Ľ–ł –ł–∑–ľ–Ķ—Ä–Ķ–Ĺ–ł—Ź –≤ –ľ–Ķ—Ā—ā–Ĺ–ĺ–ľ —ā–ĺ–Ņ–ł–ļ–Ķ –Ď–Ķ–Ĺ—á–ľ–į—Ä–ļ–į –§–ĺ—Ä—ā —Ā–ł—Ā—ā–Ķ–ľ)

P.S. –Ę–į–Ī–Ľ–ł—Ü–į –Ĺ–į —Ā–į–Ļ—ā–Ķ –ł–∑–ľ–Ķ—Ä–Ķ–Ĺ–ł—Ź –ī–Ľ—Ź —Ä–į–∑–Ĺ—č—Ö –ļ—Ä–ł—Ā—ā–į–Ľ–ĺ–≤ https://www.eembc.org/coremark/scores.php

–ö–ĺ–≥–ī–į —ā–ĺ –≤ —ć—ā–ĺ–ľ –Ď–Ķ–Ĺ—á–Ķ –Ī—č–Ľ–ł –ł –ī–į–Ĺ–Ĺ—č–Ķ –Ņ–ĺ —Ā—ā–Ķ–ļ–ĺ–≤–ĺ–ľ—É –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É [url=https://www.dnd.utwente.nl/~tim/colorforth/PTSC/IGNITE_Processor_Reference_Manual.pdf]PSC1000 Ignite.pdf[/url] (–ĺ—ā Patriot Scientific)

[url=https://www.dnd.utwente.nl/~tim/colorforth/PTSC/igniteIP_data%20sheet_20050506.pdf]igniteIP_20050506.pdf[/url]

(0,13 –ľ–ł–ļ—Ä–ĺ–Ĺ 600–ú–ď—Ü)

[url=https://web.archive.org/web/20040612144102/http://ptsc.com:80/Download/download/IGNITE_C_Tools.html]–Ē–Ľ—Ź PSC1000 Ignite –Ī—č–Ľ –ł –°–ł –ļ–ĺ–ľ–Ņ–ł–Ľ—Ź–ĺ—Ä –ī–Ľ—Ź Win/Linux[/url] (–≤ –í–Ķ–Ī –į—Ä—Ö–ł–≤–Ķ –ĺ—ā 2003–≥ –Ĺ–Ķ —Ā–ĺ—Ö—Ä–į–Ĺ–Ķ–Ĺ—č)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –í—ā —Ā–Ķ–Ĺ 05, 2023 04:34 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

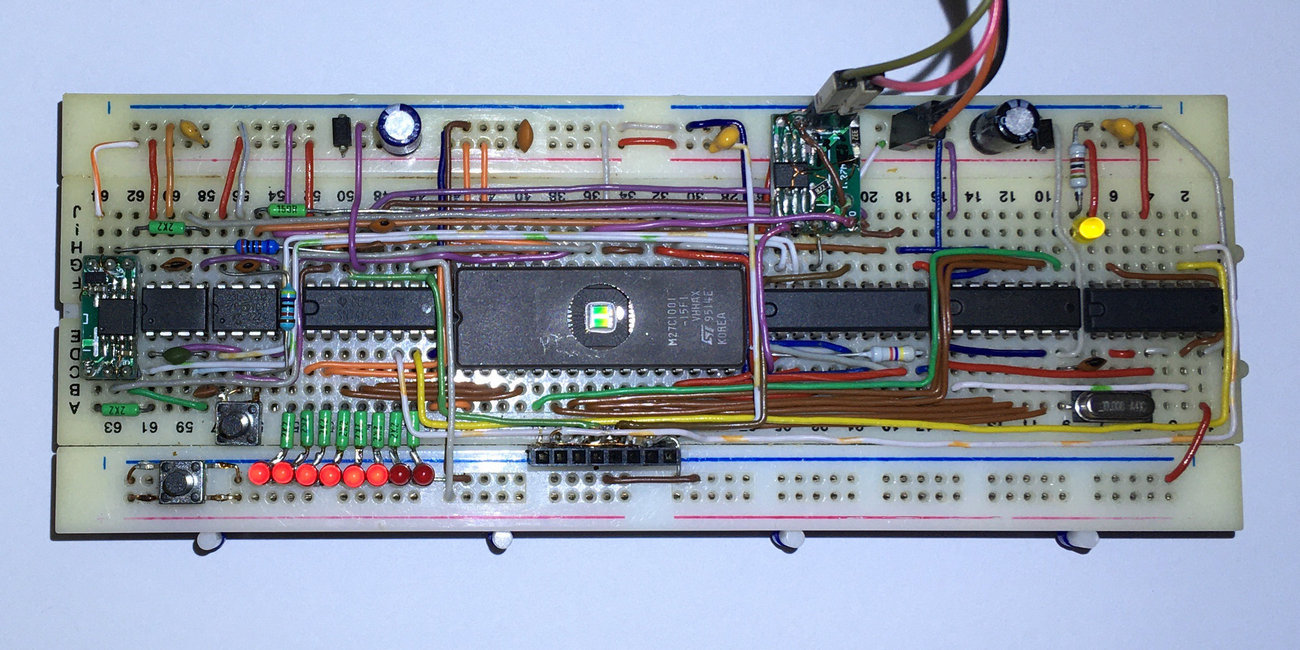

–Ě–Ķ –§–ĺ—Ä—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, –Ĺ–ĺ –į–≤—ā–ĺ—Ä—Ā–ļ–ł–Ļ –Ņ—Ä–ĺ–Ķ–ļ—ā 16-—ā–ł –Ī–ł—ā–Ĺ–ĺ–≥–ĺ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –Ĺ–į –ľ–ł–Ĺ–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–ľ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–Ķ –ī–ł—Ā–ļ—Ä–Ķ—ā–Ĺ—č—Ö TTL –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ (8-–ľ–ł) (–Ņ—Ä–ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł–ł 1-–≥–ĺ –Ī–ł—ā–Ĺ–ĺ–≥–ĺ ALU –ł –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ –Ņ–į–ľ—Ź—ā–ł –ī–Ľ—Ź –ł—Ö –ľ–ł–Ĺ–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–≥–ĺ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–į)  –ü—Ä–ĺ–Ķ–ļ—ā–ł—Ä—É–Ķ–ľ —Ā–į–ľ–ĺ–ī–Ķ–Ľ—Ć–Ĺ—č–Ļ 16-–Ī–ł—ā–Ĺ—č–Ļ CPU –≤ 2023 –≥–ĺ–ī—É –ü—Ä–ĺ–Ķ–ļ—ā–ł—Ä—É–Ķ–ľ —Ā–į–ľ–ĺ–ī–Ķ–Ľ—Ć–Ĺ—č–Ļ 16-–Ī–ł—ā–Ĺ—č–Ļ CPU –≤ 2023 –≥–ĺ–ī—É  –¶–ł—ā–į—ā–į: –Ē–Ľ—Ź —Ā–ĺ–∑–ī–į–Ĺ–ł—Ź 16-–Ī–ł—ā–Ĺ–ĺ–≥–ĺ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–≥–ĺ CPU –Ĺ—É–∂–Ĺ–ĺ –≤—Ā–Ķ–≥–ĺ 8 –ł–Ĺ—ā–Ķ–≥—Ä–į–Ľ—Ć–Ĺ—č—Ö —Ā—Ö–Ķ–ľ, –≤–ļ–Ľ—é—á–į—Ź –Ņ–į–ľ—Ź—ā—Ć –ł —ā–į–ļ—ā–ĺ–≤—č–Ļ –≥–Ķ–Ĺ–Ķ—Ä–į—ā–ĺ—Ä. –ě–Ĺ –ł–ľ–Ķ–Ķ—ā 128 –ö–Ď SRAM, 768 –ö–Ď FLASH –ł –Ķ–≥–ĺ –ľ–ĺ–∂–Ĺ–ĺ —Ä–į–∑–≥–ĺ–Ĺ—Ź—ā—Ć –ī–ĺ 10 –ú–ď—Ü. –ě–Ĺ —Ā–ĺ–ī–Ķ—Ä–∂–ł—ā —ā–ĺ–Ľ—Ć–ļ–ĺ 1-–Ī–ł—ā–Ĺ–ĺ–Ķ –ź–õ–£, –ĺ–ī–Ĺ–į–ļ–ĺ –Ī–ĺ–Ľ—Ć—ą–ł–Ĺ—Ā—ā–≤–ĺ –ł–∑ –Ķ–≥–ĺ 52 –ļ–ĺ–ľ–į–Ĺ–ī —Ä–į–Ī–ĺ—ā–į–Ķ—ā —Ā 16-–Ī–ł—ā–Ĺ—č–ľ–ł –∑–Ĺ–į—á–Ķ–Ĺ–ł—Ź–ľ–ł (–Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ). –Ě–į —Ā–≤–ĺ–Ķ–Ļ –ľ–į–ļ—Ā–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–Ļ —Ā–ļ–ĺ—Ä–ĺ—Ā—ā–ł –ĺ–Ĺ –ł—Ā–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –Ņ—Ä–ł–ľ–Ķ—Ä–Ĺ–ĺ 12 —ā—č—Ā—Ź—á –ļ–ĺ–ľ–į–Ĺ–ī –≤ —Ā–Ķ–ļ—É–Ĺ–ī—É (0,012 MIPS) –ł, —Ā—Ä–Ķ–ī–ł –Ņ—Ä–ĺ—á–Ķ–≥–ĺ, —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ķ–Ĺ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –Ņ–ĺ—ā–ĺ–ļ–ĺ–≤—É—é –Ņ–Ķ—Ä–Ķ–ī–į—á—É –≤–ł–ī–Ķ–ĺ –Ĺ–į –Ė–ö-–ī–ł—Ā–Ņ–Ľ–Ķ–Ļ –Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ PCD8544 (Nokia 5110) —Ā —á–į—Ā—ā–ĺ—ā–ĺ–Ļ –Ņ—Ä–ł–ľ–Ķ—Ä–Ĺ–ĺ 10 FPS. P.S. –ė–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ĺ–ĺ, —á—ā–ĺ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ —Ą–Ľ—ć—ą –Ņ–į–ľ—Ź—ā–ł –∑–į 100–ú–ď—Ü –Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä 25q32 –Ĺ–ĺ —É—ā–ł–Ľ–ł–∑–ł—Ä–ĺ–į—ā—Ć –ł—Ö —Ā–ļ–ĺ—Ä–ĺ—Ā—ā–Ĺ—č–Ķ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā–ł, –≤–Ķ—Ä–ĺ—Ź—ā–Ĺ–ĺ –ľ–ĺ–∂–Ĺ–ĺ —ā–ĺ–Ľ—Ć–ļ–ĺ —Ā FPGA –ł/–ł–Ľ–ł –≥–ī–Ķ –ļ –Ĺ–ł–ľ —Ā–ī–Ķ–Ľ–į–Ĺ–į –į–Ņ–Ņ–į—Ä–į—ā–Ĺ–į—Ź –Ņ–ĺ–ī–ī–Ķ—Ä–∂–ļ–į Quad-SPI (QSPI) –ė—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–Ĺ–į—Ź –≤ –Ņ—Ä–ĺ–Ķ–ļ—ā–Ķ –≤—č—ą–Ķ W25Q80 —ā–ĺ–∂–Ķ –Ņ–ĺ—Ö–ĺ–∂–Ķ —Ā —ā–į–ļ–ł–ľ–ł —Ö–į—Ä–į–ļ—ā–Ķ—Ä–ł—Ā—ā–ł–ļ–į–ľ–ł (6–Ĺ—Ā - –ľ–į–ļ—Ā–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–Ķ –≤—Ä–Ķ–ľ—Ź –ī–ĺ—Ā—ā—É–Ņ–į) –ü–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–į—Ź SRAM –Ņ–į–ľ—Ź—ā—Ć 23LC512 (–≤ –Ņ—Ä–ĺ–Ķ–ļ—ā–Ķ 2-–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č) –ź, –∑–ī–Ķ—Ā—Ć BIT SERIAL CPU and TOOL-CHAIN–Ĺ–į FPGA —Ā –§–ĺ—Ä—ā.  –Ě–Ķ –§–ĺ—Ä—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, –Ĺ–ĺ –į–≤—ā–ĺ—Ä—Ā–ļ–ł–Ļ –Ņ—Ä–ĺ–Ķ–ļ—ā 16-—ā–ł –Ī–ł—ā–Ĺ–ĺ–≥–ĺ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –Ĺ–į –ľ–ł–Ĺ–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–ľ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–Ķ –ī–ł—Ā–ļ—Ä–Ķ—ā–Ĺ—č—Ö TTL –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ (8-–ľ–ł)

(–Ņ—Ä–ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł–ł 1-–≥–ĺ –Ī–ł—ā–Ĺ–ĺ–≥–ĺ ALU –ł –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ –Ņ–į–ľ—Ź—ā–ł –ī–Ľ—Ź –ł—Ö –ľ–ł–Ĺ–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–≥–ĺ –ļ–ĺ–Ľ–ł—á–Ķ—Ā—ā–≤–į) :)

[url=https://habr.com/ru/companies/ruvds/articles/757854/]–ü—Ä–ĺ–Ķ–ļ—ā–ł—Ä—É–Ķ–ľ —Ā–į–ľ–ĺ–ī–Ķ–Ľ—Ć–Ĺ—č–Ļ 16-–Ī–ł—ā–Ĺ—č–Ļ CPU –≤ 2023 –≥–ĺ–ī—É[/url]

[img]https://habrastorage.org/webt/rk/ex/zi/rkexziknaprjh5sb3wqbkzp63gu.jpeg[/img]

[quote]–Ē–Ľ—Ź —Ā–ĺ–∑–ī–į–Ĺ–ł—Ź 16-–Ī–ł—ā–Ĺ–ĺ–≥–ĺ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–≥–ĺ CPU –Ĺ—É–∂–Ĺ–ĺ –≤—Ā–Ķ–≥–ĺ 8 –ł–Ĺ—ā–Ķ–≥—Ä–į–Ľ—Ć–Ĺ—č—Ö —Ā—Ö–Ķ–ľ, –≤–ļ–Ľ—é—á–į—Ź –Ņ–į–ľ—Ź—ā—Ć –ł —ā–į–ļ—ā–ĺ–≤—č–Ļ –≥–Ķ–Ĺ–Ķ—Ä–į—ā–ĺ—Ä. –ě–Ĺ –ł–ľ–Ķ–Ķ—ā 128 –ö–Ď SRAM, 768 –ö–Ď FLASH –ł –Ķ–≥–ĺ –ľ–ĺ–∂–Ĺ–ĺ —Ä–į–∑–≥–ĺ–Ĺ—Ź—ā—Ć –ī–ĺ 10 –ú–ď—Ü. –ě–Ĺ —Ā–ĺ–ī–Ķ—Ä–∂–ł—ā —ā–ĺ–Ľ—Ć–ļ–ĺ 1-–Ī–ł—ā–Ĺ–ĺ–Ķ –ź–õ–£, –ĺ–ī–Ĺ–į–ļ–ĺ –Ī–ĺ–Ľ—Ć—ą–ł–Ĺ—Ā—ā–≤–ĺ –ł–∑ –Ķ–≥–ĺ 52 –ļ–ĺ–ľ–į–Ĺ–ī —Ä–į–Ī–ĺ—ā–į–Ķ—ā —Ā 16-–Ī–ł—ā–Ĺ—č–ľ–ł –∑–Ĺ–į—á–Ķ–Ĺ–ł—Ź–ľ–ł (–Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ). –Ě–į —Ā–≤–ĺ–Ķ–Ļ –ľ–į–ļ—Ā–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–Ļ —Ā–ļ–ĺ—Ä–ĺ—Ā—ā–ł –ĺ–Ĺ –ł—Ā–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –Ņ—Ä–ł–ľ–Ķ—Ä–Ĺ–ĺ 12 —ā—č—Ā—Ź—á –ļ–ĺ–ľ–į–Ĺ–ī –≤ —Ā–Ķ–ļ—É–Ĺ–ī—É (0,012 MIPS) –ł, —Ā—Ä–Ķ–ī–ł –Ņ—Ä–ĺ—á–Ķ–≥–ĺ, —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ķ–Ĺ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –Ņ–ĺ—ā–ĺ–ļ–ĺ–≤—É—é –Ņ–Ķ—Ä–Ķ–ī–į—á—É –≤–ł–ī–Ķ–ĺ –Ĺ–į –Ė–ö-–ī–ł—Ā–Ņ–Ľ–Ķ–Ļ –Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ PCD8544 (Nokia 5110) —Ā —á–į—Ā—ā–ĺ—ā–ĺ–Ļ –Ņ—Ä–ł–ľ–Ķ—Ä–Ĺ–ĺ 10 FPS.[/quote]

P.S. –ė–Ĺ—ā–Ķ—Ä–Ķ—Ā–Ĺ–ĺ, —á—ā–ĺ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ —Ą–Ľ—ć—ą –Ņ–į–ľ—Ź—ā–ł –∑–į 100–ú–ď—Ü

–Ě–į–Ņ—Ä–ł–ľ–Ķ—Ä [url=https://www.chipdip.ru/search?searchtext=25q32]25q32[/url] –Ĺ–ĺ —É—ā–ł–Ľ–ł–∑–ł—Ä–ĺ–į—ā—Ć –ł—Ö —Ā–ļ–ĺ—Ä–ĺ—Ā—ā–Ĺ—č–Ķ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā–ł,

–≤–Ķ—Ä–ĺ—Ź—ā–Ĺ–ĺ –ľ–ĺ–∂–Ĺ–ĺ —ā–ĺ–Ľ—Ć–ļ–ĺ —Ā FPGA –ł/–ł–Ľ–ł –≥–ī–Ķ –ļ –Ĺ–ł–ľ —Ā–ī–Ķ–Ľ–į–Ĺ–į –į–Ņ–Ņ–į—Ä–į—ā–Ĺ–į—Ź –Ņ–ĺ–ī–ī–Ķ—Ä–∂–ļ–į Quad-SPI (QSPI)

–ė—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–Ĺ–į—Ź –≤ –Ņ—Ä–ĺ–Ķ–ļ—ā–Ķ –≤—č—ą–Ķ [url=https://www.chipdip.ru/search?searchtext=W25Q80]W25Q80[/url] —ā–ĺ–∂–Ķ –Ņ–ĺ—Ö–ĺ–∂–Ķ —Ā —ā–į–ļ–ł–ľ–ł —Ö–į—Ä–į–ļ—ā–Ķ—Ä–ł—Ā—ā–ł–ļ–į–ľ–ł (6–Ĺ—Ā - –ľ–į–ļ—Ā–ł–ľ–į–Ľ—Ć–Ĺ–ĺ–Ķ –≤—Ä–Ķ–ľ—Ź –ī–ĺ—Ā—ā—É–Ņ–į)

–ü–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–į—Ź SRAM –Ņ–į–ľ—Ź—ā—Ć [url=https://www.chipdip.ru/search?searchtext=23LC512]23LC512[/url] (–≤ –Ņ—Ä–ĺ–Ķ–ļ—ā–Ķ 2-–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č)

–ź, –∑–ī–Ķ—Ā—Ć [url=https://github.com/howerj/bit-serial]BIT SERIAL CPU and TOOL-CHAIN[/url]–Ĺ–į FPGA —Ā –§–ĺ—Ä—ā. :)

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –ß—ā –į–≤–≥ 31, 2023 11:31 |

|

|

|

|

|

| |

–ó–į–≥–ĺ–Ľ–ĺ–≤–ĺ–ļ —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł—Ź: |

Re: –ö–į–ļ —Ā–ī–Ķ–Ľ–į—ā—Ć —Ą–ĺ—Ä—ā-–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä 2022 |

|

|

Total Vacuum –Ņ–ł—Ā–į–Ľ(–į): –Ě—É –į –ļ—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ 6-–Ī–ł—ā–Ĺ–į—Ź –ļ–ĺ–ľ–į–Ĺ–ī–į –Ņ–ĺ–∑–≤–ĺ–Ľ—Ź–Ķ—ā —É—ā—Ä–į–ľ–Ī–ĺ–≤–į—ā—Ć —ā—É–ī–į –≤–Ķ—Ā—Ć uf \ micro forth \ –Ę—É—ā –Ķ—Č—Ď –ī–Ľ—Ź —Ä–į–∑–ľ—č—ą–Ľ–Ķ–Ĺ–ł—Ź –ľ–ĺ–∂–Ĺ–ĺ –≥–Ľ—Ź–Ĺ—É—ā—Ć –Ĺ–į —ć–∑–ĺ—ā–Ķ—Ä—á–Ķ—Ā–ļ–ł–Ļ —Ā—ā–Ķ–ļ–ĺ–≤—č–Ļ —Ź–∑—č–ļ GolfScript  (–ľ–ĺ–∂–Ķ—ā —á—ā–ĺ —ā–ĺ –≤ –Ķ–≥–ĺ –ī–ł–∑–į–Ļ–Ĺ–Ķ –Ņ–ĺ–Ĺ—Ä–į–≤–ł—ā—Ā—Ź) P.S. –Ě–Ķ–ľ–Ĺ–ĺ–≥–ĺ —Ä–Ķ—ą—Ď–Ĺ–Ĺ—č—Ö –Ĺ–į –Ĺ—Ď–ľ –∑–į–ī–į—á https://rosettacode.org/wiki/Category:Golfscript–Ď—č–≤–į–Ķ—ā –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ł –ī–Ľ—Ź —Ā–ĺ—Ā—ā–į–≤–Ľ–Ķ–Ĺ–ł—Ź —Ä–Ķ—ą–Ķ–Ĺ–ł–Ļ –Ĺ–į https://codegolf.stackexchange.com/[quote="Total Vacuum"] –Ě—É –į –ļ—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ 6-–Ī–ł—ā–Ĺ–į—Ź –ļ–ĺ–ľ–į–Ĺ–ī–į –Ņ–ĺ–∑–≤–ĺ–Ľ—Ź–Ķ—ā —É—ā—Ä–į–ľ–Ī–ĺ–≤–į—ā—Ć —ā—É–ī–į –≤–Ķ—Ā—Ć uf \ micro forth \[/quote]

–Ę—É—ā –Ķ—Č—Ď –ī–Ľ—Ź —Ä–į–∑–ľ—č—ą–Ľ–Ķ–Ĺ–ł—Ź –ľ–ĺ–∂–Ĺ–ĺ –≥–Ľ—Ź–Ĺ—É—ā—Ć –Ĺ–į —ć–∑–ĺ—ā–Ķ—Ä—á–Ķ—Ā–ļ–ł–Ļ —Ā—ā–Ķ–ļ–ĺ–≤—č–Ļ —Ź–∑—č–ļ [url=http://www.golfscript.com/golfscript/tutorial.html]GolfScript[/url] :) (–ľ–ĺ–∂–Ķ—ā —á—ā–ĺ —ā–ĺ –≤ –Ķ–≥–ĺ –ī–ł–∑–į–Ļ–Ĺ–Ķ –Ņ–ĺ–Ĺ—Ä–į–≤–ł—ā—Ā—Ź)

P.S. –Ě–Ķ–ľ–Ĺ–ĺ–≥–ĺ —Ä–Ķ—ą—Ď–Ĺ–Ĺ—č—Ö –Ĺ–į –Ĺ—Ď–ľ –∑–į–ī–į—á [url=https://rosettacode.org/wiki/Category:Golfscript]https://rosettacode.org/wiki/Category:Golfscript[/url]

–Ď—č–≤–į–Ķ—ā –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ł –ī–Ľ—Ź —Ā–ĺ—Ā—ā–į–≤–Ľ–Ķ–Ĺ–ł—Ź —Ä–Ķ—ą–Ķ–Ĺ–ł–Ļ –Ĺ–į https://codegolf.stackexchange.com/

|

|

|

|

–Ē–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–ĺ: –í—Ā –į–≤–≥ 13, 2023 14:00 |

|

|

|

|